実験室のINDEXに戻る

実験室のINDEXに戻る![]() 実験の目的

実験の目的

机上で悩んだ時は実験が一番。

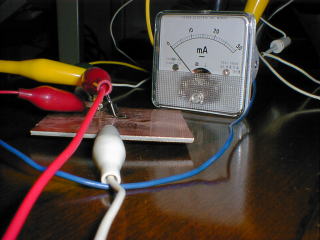

![]() 実験の様子

実験の様子

生基板を小さく切って、Ugly Construction手法でP-JFETを半田付け。

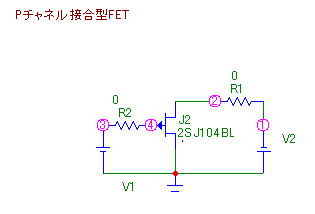

![]() Pチャネル接合型FET 2SJ104BLのId-Vds の測定

Pチャネル接合型FET 2SJ104BLのId-Vds の測定

ドレイン電圧に対する、ドレイン電流の変化を測定することと、

ゲート電圧を印加してピンチオフ電圧を確認した。

![]()

Id-Vdsの測定実験

[実験の目的]

MicroCapで接合型FETを使ったアナログスイッチの実験(シュミレート)をしてみたのだが、

逆方向VDSの極性側でトンネル効果のようなIdsの大電流が見られたのと、ピンチオフ特性

(またはカットオフ特性)が得られずに悩んでしまった(Vgsによってドレイン電流が制御できない)。

そこでバラックを組み立てて2SJ104BLのId-Vds特性を実際に計測してみた。

抵抗R1、R2はゼロΩ

V1はVgs設定用、V2はVds設定用

V2のマイナス側とD(ドレイン)間に直流電流計(20mA)を接続してIdsを測定した。

May31, 2004

![]() INDEXに戻る

INDEXに戻る

実験の様子

生基板を小さく切ってP-JFETを半田付けした。

Ugly Construction手法で実験。

![]() INDEXに戻る

INDEXに戻る

Pチャネル接合型FET 2SJ104BLのId-Vds の測定

| Vds(-) 順方向 | |||

| Vds(mV) | Id(mA) | Vgs(V) | |

| -31.5 | -1 | 0 | |

| -81.4 | -2 | 0 | |

| -145.2 | -3 | 0 | |

| -214 | -4 | 0 | |

| -309 | -5 | 0 | |

| -484 | -4 | 0 | |

| -832 | -5 | 0 | |

| -1257 | -10 | 0 | |

| -309 | -5 | 0 | VGSoff ピンチオフ電圧 (カットオフ) |

| -309 | -1 | 0.203 | |

| -309 | 0 | 0.546 | |

Vdsの-309mVから-832mVの領域で負特性を示している。

原因はわかりません。逆方向Vdsで大きな電流を流してしまってからの計測だったから、FETにダメージを与えたか?

May31, 2004

| Vds(+) 逆方向 | |||

| Vds(mV) | Id(mA) | Vgs(V) | |

| 38 | 1 | 0 | |

| 77 | 2 | 0 | |

| 103 | 3 | 0 | |

| 132 | 4 | 0 | |

| 163 | 5 | 0 | |

| 284 | 10 | 0 | |

| 400 | 15 | 0 | |

| 500 | 20 | 0 | |

| 163 | 5 | 0 | VGSoff ピンチオフ電圧 (カットオフ) |

| 163 | 1 | 0.203 | |

| 163 | 0 | 0.546 | |

規格表には順方向VDS(-)のID-VDS特性だけが書かれている。

逆方向は左表のように僅かVds 500mVでId がなんと20mAも流れた。

規格表によれば2SJ104BLのIdssはmax12mA。

この実験でアナログスイッチの勘所が分かったような気がする。

![]() アナログスイッチとして使用する領域はVdsの小さな領域である。

アナログスイッチとして使用する領域はVdsの小さな領域である。

![]() Idsが2mAまではVDSの双方向で(両極性で)酷似した特性を示している。

Idsが2mAまではVDSの双方向で(両極性で)酷似した特性を示している。

May31, 2004

[参考]

三和計器のhfe/Idss測定器(型式:HFE-5)による測定結果は Idss=8.8mAであった。

![]() INDEXに戻る

INDEXに戻る

実験結果の考察

鈴木茂昭著 「アナログスイッチの使い方」に下記、キーポイントの記述があります。実験してみて鈴木氏の言わん

としている事がやっと理解できた気がする。

----------------------------------------------------------------------------------------

![]() 出典:鈴木茂昭著 「アナログスイッチの使い方」 CQ出版社

出典:鈴木茂昭著 「アナログスイッチの使い方」 CQ出版社

![]() Pチャネル型J-FETでピンチオフ電圧が4V以下の物があれば、TTLもしくはC-MOSロジックから直接ドライブでき、

Pチャネル型J-FETでピンチオフ電圧が4V以下の物があれば、TTLもしくはC-MOSロジックから直接ドライブでき、

特にスイッチドライバの考慮は不要になります。(Nチャネル型J-FETではピンチオフさせるためにゲートを負側に

スイングさせなければならないので余計に1個トランジスタが必要だし、負電源も必要.)

![]() アナログスイッチをOPアンプの入力に用いるときは仮想ゼロ点(仮想接地点)にJ-FETを配置し、VDSを十分低く

アナログスイッチをOPアンプの入力に用いるときは仮想ゼロ点(仮想接地点)にJ-FETを配置し、VDSを十分低く

保つ事が大切.理由は50Ω程度のRds(ON抵抗)ならVDSは極めて低くなりVGSはほとんど0V付近となって十分

ON状態を続けられることになる.(ピンチオフ電圧以下だから)

----------------------------------------------------------------------------------------