![]() シリアル通信モジュール(Serial Communications InterfaceModule)の使い方

シリアル通信モジュール(Serial Communications InterfaceModule)の使い方

【S08SCIV4】

シリアル通信モジュール(SCI)はUARTとも呼ばれる通信インターフェースです。通常TXとRXで全2重通信を行う事が出来ます。

TX,RX端子にRS232CトランシーバICを接続すればRS-232Cインターフェースとして動作します。同様にRS422やRS485トランシーバを接続する事で各インターフェースに対応する事が出来ます。

違いは電圧や平衡か不平衡かの違いだけです。

最もポピュラーな

ボーレート 9600

パリティー なし

スタートビット 1Bit

ストップビット 1ビット

以上の仕様で説明します。

マイコンのTX端子は待機中は1(Hi)の状態です。ビット幅はボーレートで決まります。

通信の開始はスタートビットでLowを1ビット幅だけ維持します。受信側はこのスタートビットの立下りを検出して受信処理を開始します。

LSBから順にMSBまで8ビット分のデータを1ビット幅ずつ変化させ、最後にストップビットとしてHiを1ビット幅維持します。

受信側はこのストップビットを1ビット幅検出すると受信処理を終了します。

TX出力に0x0Fという8ビットデータを送信するとオシロスコープでは上図のようになります。

LSBから送信されるので右から00001111と読む事が出来ます。

HCS08マイコンには以下の特長があります。

【送信】

プログラミングではSCIDレジスタに8ビットデータを代入するだけで自動的に送信されます。

下記の例では変数”CUSTOMCODE”という8ビットデータをSCIDに代入しています。

SCIモジュールを複数備えているマイコンではSCIxDとなり、xがSCIモジュール番号になります。

MC9S08QE128の場合SCI1DとSCI2Dになります。

/***** 送信 *****/

while(!SCIS1_TDRE); // 送信バッファ空き待

SCID = CUSTOMCODE; // カスタムコード送信

最初のwhile文は送信データレジスタSCIDが前回の送信が終了して、空になるまで待機します。

自動で送信されるので、準備が出来ている事を確認する必要があります。

【受信】

受信には二つの方法があります。一つはラジコン受信機のように受信しないと他にする事が無いので受信するまで待ち続ける受信待ちタイプです。

もう一つは受信したら割込みで受信データを保存して、普段は別の仕事をする受信割込みタイプです。

受信待ちタイプ

受信はステータスレジスタSCISレジスタのRDRFが1になったら8ビットデータがバッファーに蓄えられているのでSCIDレジスタを読めば受信データを得る事が出来ます。

下記のプログラムはアンプ付き受信機のRECEIVE関数です。連続してデータが送られてくる仕様なので途切れた時にエラーを出すようになっています。

モジュロータイマーMTIMの周期は3mSにプロセッサーエキスパートで設定してあります。受信処理でモジュロータイマーをリセットしてスタートさせます。

while文でSCIS1_RDRFが0の間、待機します。待機中にモジュロータイマーが1mSに達するとMTIM_TOFが1に変化するのでエラーカウンターを加算します。

エラーカウンターが10になったら受信をあきらめて抜けます。

受信できた場合は、変数CUSTOMCODEと比較し、一致していれば次のデータを受信します。

while文で受信待ちをする時はタイマーを使用して、一定期間受信できなかったら抜ける処理を追加する事で永久に受信待ち状態である事から抜ける事が出来ます。

下記の例ではラジコン受信機なので電波状態により受信できない場合、模型の暴走を防ぐため停止データをモータ側に送る事で安全に停止させます。

受信割込みタイプ

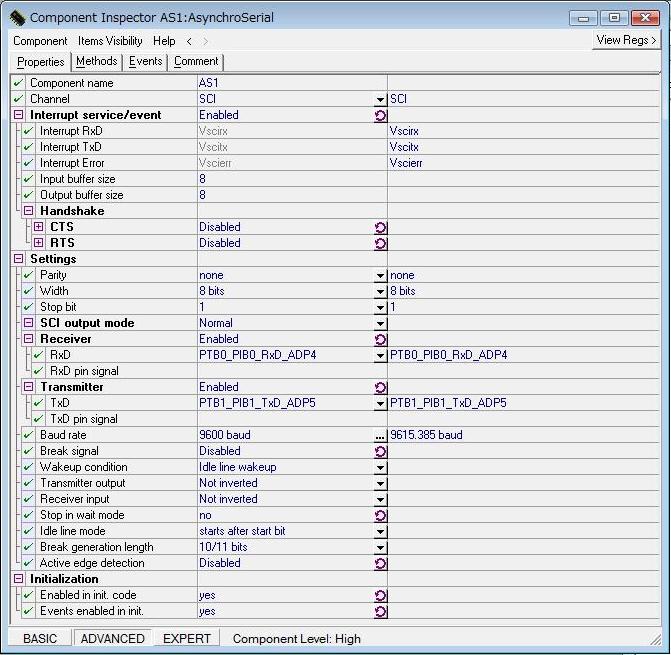

受信データを割込みで処理する場合はまず、プロセッサーエキスパートのAsyncroSerialコンポーネントの設定でInterrupt service/eventの項目をEnavleにします。

これにより3つの割込み関数(受信割込み、送信割込み、エラー割込み)がEvents.cというソースに自動生成されます。

下記はコンポーネント名CONTROLERという名前でAsyncroSerialコンポーネントにより自動生成された受信割込み処理です。

/* Write your code here ... */という行の次に割込みで行いたい処理を記述します。自動生成された部分は文字が緑色で表しています。

グローバル変数CNT_RX_FLGはデータを受信した事を示すフラグとして使用します。メインループはこのフラグをチェックして受信データが受信できたことを確認して処理します。

受信データはRecvChar()関数を使用してグローバル変数RX_BUFに格納します。

プロセッサーエキスパートはRecvChar()関数でデータを読み込むことで受信バッファーの内容が読み込まれたと判断し、次のデータを受信するします。

この関数を使用せずにRX_BUF = SCID;と記述してデータを読み込んでも、次のデータを受信しない為、次回受信時にオーバーランエラーとなります。

これを避けるためにはSCIS1をリードして、エラーがないか確認する必要があります。RecvChar()関数にはこのエラーチェックも含まれているので簡単に読み込むことができます。

受信エラーが発生した場合はOnError()関数にジャンプしてきますので適切な処理を記述します。何も記述しなければそのままメインループに戻ることになります。

次の受信割込みが発生するまでの間にメインループでRX_BUFの値を生かした処理を実行すれば問題は起きません。

しかし、次の受信が先に来てしまうとRX_BUFの内容は書き換えられてしまうので、注意が必要です。

割込みで処理する場合はmainループの1周期がどれ程の時間になるのか意識する必要があります。

** ===================================================================

** Event : CONTROLER_OnRxChar (module Events)

**

** Component : CONTROLER [AsynchroSerial]

** Description :

** This event is called after a correct character is

** received.

** The event is available only when the <Interrupt

** service/event> property is enabled and either the

** <Receiver> property is enabled or the <SCI output mode>

** property (if supported) is set to Single-wire mode.

** Parameters : None

** Returns : Nothing

** ===================================================================

*/

void CONTROLER_OnRxChar(void)

{

/* Write your code here ... */

extern bool CNT_RX_FLG;

extern byte RX_BUF;

extern byte ERR;

ERR = RecvChar(&RX_BUF);

CNT_RX_FLG = 1;

}

プロセッサーエキスパートで自動生成される割込み処理は上記の場合、Vector.c→CONTROLER.c→Event.cの順番で行われます。

Vector.cでは下記のように記述されます。

CONTROLER_InterruptRx, /* Int.no. 22 Vsci2rx (at FFD2) Used */

受信割込みが発生した時、ISR(CONTROLER_InterruptRx)という関数で処理せよと言う事になります。

このISR(CONTROLER_InterruptRx)と言う関数が記述されるのがCONTROLER.cです。

/** ###################################################################

** THIS COMPONENT MODULE IS GENERATED BY THE TOOL. DO NOT MODIFY IT.

** Filename : Vectors.C

** Project : MAIN_BOARD

** Processor : MC9S08QE128CLH

** Version : Component 01.002, Driver 01.35, CPU db: 3.00.060

** Compiler : CodeWarrior HCS08 C Compiler

** Date/Time : 2011/09/08, 10:07

** Abstract :

** This bean "MC9S08QE128_64" contains initialization of the

** CPU and provides basic methods and events for CPU core

** settings.

** Settings :

**

**

** Copyright : 1997 - 2009 Freescale Semiconductor, Inc. All Rights Reserved.

**

** http : www.freescale.com

** mail : support@freescale.com

** ###################################################################*/

#include "Cpu.h"

#include "CAMERA.h"

#include "CONTROLER.h"

#include "RX_RE.h"

#include "RX_DE.h"

#include "TX_RE.h"

#include "TX_DE.h"

extern near void _EntryPoint(void);

void (* near const _vect[])(void) @0xFFC0 = { /* Interrupt vector table */

Cpu_Interrupt, /* Int.no. 31 Vtpm3ovf (at FFC0) Unassigned */

Cpu_Interrupt, /* Int.no. 30 Vtpm3ch5 (at FFC2) Unassigned */

Cpu_Interrupt, /* Int.no. 29 Vtpm3ch4 (at FFC4) Unassigned */

Cpu_Interrupt, /* Int.no. 28 Vtpm3ch3 (at FFC6) Unassigned */

Cpu_Interrupt, /* Int.no. 27 Vtpm3ch2 (at FFC8) Unassigned */

Cpu_Interrupt, /* Int.no. 26 Vtpm3ch1 (at FFCA) Unassigned */

Cpu_Interrupt, /* Int.no. 25 Vtpm3ch0 (at FFCC) Unassigned */

Cpu_Interrupt, /* Int.no. 24 Vrtc (at FFCE) Unassigned */

CONTROLER_InterruptTx, /* Int.no. 23 Vsci2tx (at FFD0) Used */

CONTROLER_InterruptRx, /* Int.no. 22 Vsci2rx (at FFD2) Used */

CONTROLER_InterruptError, /* Int.no. 21 Vsci2err (at FFD4) Used */

Cpu_Interrupt, /* Int.no. 20 Vacmpx (at FFD6) Unassigned */

Cpu_Interrupt, /* Int.no. 19 Vadc (at FFD8) Unassigned */

Cpu_Interrupt, /* Int.no. 18 Vkeyboard (at FFDA) Unassigned */

Cpu_Interrupt, /* Int.no. 17 Viicx (at FFDC) Unassigned */

CAMERA_InterruptTx, /* Int.no. 16 Vsci1tx (at FFDE) Used */

CAMERA_InterruptRx, /* Int.no. 15 Vsci1rx (at FFE0) Used */

CAMERA_InterruptError, /* Int.no. 14 Vsci1err (at FFE2) Used */

Cpu_Interrupt, /* Int.no. 13 Vspi1 (at FFE4) Unassigned */

Cpu_Interrupt, /* Int.no. 12 Vspi2 (at FFE6) Unassigned */

Cpu_Interrupt, /* Int.no. 11 Vtpm2ovf (at FFE8) Unassigned */

Cpu_Interrupt, /* Int.no. 10 Vtpm2ch2 (at FFEA) Unassigned */

Cpu_Interrupt, /* Int.no. 9 Vtpm2ch1 (at FFEC) Unassigned */

Cpu_Interrupt, /* Int.no. 8 Vtpm2ch0 (at FFEE) Unassigned */

Cpu_Interrupt, /* Int.no. 7 Vtpm1ovf (at FFF0) Unassigned */

Cpu_Interrupt, /* Int.no. 6 Vtpm1ch2 (at FFF2) Unassigned */

Cpu_Interrupt, /* Int.no. 5 Vtpm1ch1 (at FFF4) Unassigned */

Cpu_Interrupt, /* Int.no. 4 Vtpm1ch0 (at FFF6) Unassigned */

Cpu_Interrupt, /* Int.no. 3 Vlvd (at FFF8) Unassigned */

Cpu_Interrupt, /* Int.no. 2 Virq (at FFFA) Unassigned */

Cpu_Interrupt, /* Int.no. 1 Vswi (at FFFC) Unassigned */

_EntryPoint /* Int.no. 0 Vreset (at FFFE) Reset vector */

};

/*

** ###################################################################

**

** This file was created by Processor Expert 3.07 [04.34]

** for the Freescale HCS08 series of microcontrollers.

**

** ###################################################################

*/

下記がCONTROLER.cの割込み処理関数ISR(CONTROLER_InterruptRx)です。

ここでは受信エラーをチェックする為、SCI2S1をStatRegに代入し、受信データレジスタSCI2Dの値をCONTROLER_TComData

Dataに代入しています。

この処理は実は大変重要でSCIxS1をリードした後にSCIxDをリードすると言う処理を行わないと受信フラグSCIxS1_TDREがクリアされません。

エラーが無い場合、最終行のCONTROLER_OnRxChar(); /* If yes then invoke user event */によりEvent.cのCONTROLER_OnRxChar()関数へ飛びます。

** ===================================================================

** Method : CONTROLER_InterruptRx (component AsynchroSerial)

**

** Description :

** The method services the receive interrupt of the selected

** peripheral(s) and eventually invokes the bean's event(s).

** This method is internal. It is used by Processor Expert only.

** ===================================================================

*/

#define ON_ERROR 0x01

#define ON_FULL_RX 0x02

#define ON_RX_CHAR 0x04

#define ON_IDLE_CHAR 0x08

#define ON_RX_CHAR_EXT 0x10

ISR(CONTROLER_InterruptRx)

{

byte OnFlags = 0x00; /* Temporary variable for flags */

byte StatReg = SCI2S1; /* Temporary variable for status flags */

CONTROLER_TComData Data = SCI2D; /* Read data from the receiver into temporary

variable for data */

if (SerFlag & CHAR_IN_RX) { /* Is any char already present in the

receive buffer? */

SerFlag |= OVERRUN_ERR; /* If yes then set flag OVERRUN_ERR */

OnFlags |= ON_ERROR; /* Set flag "OnError" */

} else {

BufferRead = Data; /* Copy data into global buffer variable */

SerFlag |= CHAR_IN_RX; /* Set flag "char in RX buffer" */

OnFlags |= ON_RX_CHAR; /* Set flag "OnRxChar" */

}

if (OnFlags & ON_ERROR) { /* Is OnError flag set? */

CONTROLER_OnError(); /* If yes then invoke user event */

}

else {

if (OnFlags & ON_RX_CHAR) { /* Is OnRxChar flag set? */

CONTROLER_OnRxChar(); /* If yes then invoke user event */

}

}

下記はmain.cに割込み処理関数を記述する場合の例です。プロセッサーエキスパートの初期設定コンポーネントから通信コーポーネントの割込みを有効にして割込みベクターの飛び先をOnRXに設定しています。受信割込みが発生しているので受信完了フラグSCI2S1_RDRFをif文で見る必要が無いようですが、RDRFをクリアする為にSCIxS1を一度リードしてからSCIxDをリードするという作業が必要なのでif文でSCIxS1をリードしています。下記の例では受信データがffの時RX_FLGがセットされます。

可変バイト長データの受信ではこの様にRX_DATAを配列にして格納し、受信した文字数はCHR_CNTにより得る事が出来ます。可変バイト長の場合、受信データがある値がデータ終了を意味します。下記の例ではffが終了を意味するデータです。

固定バイト長の場合は変数CHR_CNTを見て、規定バイトに達したら次の処理に移行するようにプログラムします。

//*********************************************************

//* 受信関数(割込み)

//*********************************************************

ISR (OnRX)

{

if (SCI2S1_RDRF)

{

RX_DATA[CHR_CNT] = SCI2D;

if (RX_DATA[CHR_CNT] == 0xff)

{

CHR_CNT = 0;

RX_FLG = 1;

}

else CHR_CNT = CHR_CNT + 1;

}

}

![]() SCI関連レジスタ

SCI関連レジスタ

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| SCIxBDH | LBKDIE | RXEDGIE | --- | SBR12 | SBR11 | SBR10 | SBR9 | SBR8 |

| SCIxBDL | SBR7 | SBR6 | SBR5 | SBR4 | SBR3 | SBR2 | SBR1 | SBR0 |

| SCIxC1 | LOOPS | SCISWAI | RSRC | M | WAKE | ILT | PE | PT |

| SCIxC2 | TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

| SCIxS1 | TDRE | TC | RDRF | IDLE | OR | NF | FE | PF |

| SCIxS2 | LBKDIF | RXEDGIF | --- | RXINV | RWUID | BRK13 | LBKDE | RAF |

| SCIxC3 | R8 | T8 | TXDIR | TXINV | ORIE | NEIE | FEIE | PEIE |

| SCIxD | R7/T7 | R6/T6 | R5/T5 | R4/T4 | R3/T3 | R2/T2 | R1/T1 | R0/T0 |

【SCIxBDH、SCIxBDL】SCI ボーレート・レジスタ(SCI Baud Rate Registers)

7 6 5 4 3 2 1 0 SCIxBDH LBKDIE RXEDGIE --- SBR12 SBR11 SBR10 SBR9 SBR8 R/W R/W R/W R R/W R/W R/W R/W R/W RESET 0 0 0 0 0 0 0 0 SCIxBDL SBR7 SBR6 SBR5 SBR4 SBR3 SBR2 SBR1 SBR0 R/W R/W R/W R/W R/W R/W R/W R/W R/W RESET 0 0 0 0 0 1 0 0

bit 7[LBKDIE]LIN ブレーク検出割込みイネーブル(LBKDIF 用)(LIN Break Detect Interrupt Enable)

LIN ブレーク検出で割込みを許可するか設定します。

0 = LBKDIF からのハードウェア割込みはディセーブル(ポーリングを使用)。

1 = LBKDIF フラグが1 ならハードウェア割込みが要求される。

記述例

/***** 初期設定 *****/

SCI1BDH_LBKDIE = 1; // LINブレークで割込みを許可

bit 6[RXEDGIE]RxD ピンのアクティブ・エッジ割込みフラグ(RxD Input Active Edge Interrupt Enable)

RXEDGIF は、RxD ピンでアクティブ・エッジ(RXINV = 0 なら立ち下り、RXINV = 1 なら立ち上り)が発生するとセットされます。

RXEDGIF は1 をライトするとクリアされます。

0 = 受信ピンでアクティブ・エッジは検出されていない。

1 = 受信ピンでアクティブ・エッジを検出。

記述例

/***** 初期設定 *****/

if (SCI1BDH_RXEDGIE) EDGE_FLG = 1; // アクティブエッジ検出フラグセット

bit 4-0[SCIxBDH]ボーレート・モジュロ分周値(Baud Rate Modulo Divisor)

bit 7-0[SCIxBDL]

これらの13 ビットは、SCI ボーレート・ジェネレータのモジュロ分周値を設定します。

SBR[12:0] の13 ビットをまとめてBR と呼びます。BR = 0 ならSCI ボーレート・ジェネレータはディセーブルで、供給電流は減少します。

BR = 1 〜 8191 なら、SCI ボーレートはBUSCLK/(16xBR) で求められます。

以下の記述例はBUSCLKが8MHzの時にボーレート9600に設定する例です。

0x34は十進数では52ですから分母は16×52=832。分子は8MHzですから8MHz / 832 = 9615.385

9600に対して誤差0.16%となります。ビット幅は1秒 / 9615.385 = 104uS。

データビット8bit、START・STOPは1bitとすると1byte幅は10bitですから、1.04mSとなります。

記述例

/***** 初期設定 *****/

SCI1BDH = 0x00; /* Set high divisor register (enable device) */

SCI1BDL = 0x34; /* Set low divisor register (enable device) */

// 8MHz / (16 * 52) = 9615.385 (9600)誤差0.16%

【SCIxC1】SCI 制御レジスタ1(SCI Control Register 1)

7 6 5 4 3 2 1 0 SCIxC1 LOOPS SCISWAI RSRC M WAKE ILT PE PT R/W R/W R/W R/W R/W R/W R/W R/W R/W RESET 0 0 0 0 0 0 0 0

bit 7[LOOPS]ループ・モード選択(Loop Mode Select)

レシーバ入力に接続されます。

0 = 通常動作。RxD とTxD で別のピンを使用する。

1 = ループ・モードまたはシングルワイヤ・モードで、トランスミッタ出力は内部でレシーバ入力に接続される(RSRCビットを参照)。SCI はRxD ピンを使用しない。

記述例

/***** 初期設定 *****/

SCI1C1_LOOPS = 1; // テスト用ループモードTx→Rx

bit 6[SCISWAI]ウェイト・モードでのSCI の停止(SCI Stops in Wait Mode)

0 = ウェイト・モードでSCI のクロック供給を継続する。SCI は、CPU をウェイクアップする割込みソースとして機能する。

1 = CPUがウェイト・モードならSCI のクロック供給を停止する。

記述例

/***** 初期設定 *****/

SCI1C1_SCIWAI = 1; // ウェイト・モードでSCI休止に設定

bit 5[RSRC]レシーバ・ソース選択(Receiver Source Select)

このビットは、LOOPS = 1 にセットされていなければ意味がなく効果はありません。LOOPS = 1なら、レシーバ入力は内部でTxD ピンに接続され、トランスミッタ出力まで接続されるかどうかはRSRC で決まります。

0 = LOOPS=1なら、RSRC = 0 で内部ループバック・モードが選択され、SCI はRxD ピンを使用しない。

1 = シングルワイヤSCI モードで、TxD ピンはトランスミッタ出力およびレシーバ入力に接続される。

記述例

/***** 初期設定 *****/

SCI1C1_RSRC = 1; // SCIをシングルワイヤーモードに設定

bit 4[M]9 ビットまたは8 ビット・モードの選択(9-Bit or 8-Bit Mode Select)

データビットを8bitもしくは9bitに選択する事が出来ます。

0 = スタート・ビット+ 8 データ・ビット(LSB ビット先頭)+ストップ・ビットの通常のデータ・キャラクタを使用する。

1 = レシーバおよびトランスミッタは、スタート・ビット+ 8 データ・ビット(LSB ビット先頭)+ 9 番目のデータ・ビット+ストップ・ビットの9 ビット・データ・キャラクタを使用する。

記述例

/***** 初期設定 *****/

SCI1C1_M = 0; // SCIデータ長を8bitに設定

bit 3[WAKE]レシーバ・ウェイクアップ方式の選択(Receiver Wakeup Method Select)

メッセージの末尾または次のメッセージの先頭でレシーバがウェイクアップして次のメッセージの先頭キャラクタを評価できるようにします。

0 = アイドルライン・ウェイクアップ。フル・キャラクタ・タイムを検出すると、RWU が自動的にクリアされます。

1 = アドレスマーク・ウェイクアップ。受信キャラクタの最上位ビット(M = 0 モードなら8 番目のビット、M = 1 モードなら9 番目のビット)で論理1 を検出すると、ウェイクアップします。

bit 2[ILT]アイドルライン・タイプの選択(Idle Line Type Select)

このビットを1 にセットすると、アイドルライン検出ロジックはキャラクタ末尾のストップ・ビットと論理1 のビットを、論理High レベルの10 または11 ビット・タイムとしてカウントしません。

0 = アイドル・キャラクタ・ビットのカウントをスタート・ビットの後から開始する。

1 = アイドル・キャラクタ・ビットのカウントをストップ・ビットの後から開始する。

bit 1[PE]パリティ・イネーブル(Parity Enable)

ハードウェアによるパリティの生成とチェックをイネーブルにします。パリティがイネーブルなら、データ・キャラクタの最上位ビット(8 番目または9 番目のデータ・ビット)がパリティ・ビットとして扱われます。

0 = ハードウェアによるパリティの生成またはチェックはない。

1 = パリティはイネーブル。

bit 0[PT]パリティ・タイプ(Parity Type)

パリティがイネーブルである場合(PE = 1)に偶数パリティまたは奇数パリティを選択します。奇数パリティとは、パリティ・ビットを含むデータ・キャラクタ内の論理1 の個数が奇数になることをいいます。

偶数パリティとは、パリティ・ビットを含むデータ・キャラクタ内の論理1 の個数が偶数になることをいいます。

0 = 偶数パリティ。

1 = 奇数パリティ。

【SCIxC2】SCI 制御レジスタ2(SCI Control Register 2)

7 6 5 4 3 2 1 0 SCIxC2 TIE TCIE RIE ILIE TE RE RWU SBK R/W R/W R/W R/W R/W R/W R/W R/W R/W RESET 0 0 0 0 0 0 0 0

bit 7[TIE]送信割込みイネーブル(Transmit Interrupt Enable)

0 = TDREによるハードウェア割込みはディセーブル(ポーリングを使用)。

1 = TDREフラグが1 ならハードウェア割込みが要求される。

bit 6[TCIE]送信完了割込みイネーブル(Transmission Complete Interrupt Enable)

0 = TCによるハードウェア割込みはディセーブル(ポーリングを使用)。

1 = TCフラグが1 ならハードウェア割込みが要求される。

bit 5[RIE]レシーバ割込みイネーブル(Receiver Interrupt Enable)

0 = RDRF によるハードウェア割込みはディセーブル(ポーリングを使用)。

1 = RDRF フラグが1 ならハードウェア割込みが要求される。

bit 4[ILIE]アイドルライン割込みイネーブル(Idle Line Interrupt Enable)

0 = IDLEによるハードウェア割込みはディセーブル(ポーリングを使用)。

1 = IDLEフラグが1 ならハードウェア割込みが要求される。

bit 3[TE]トランスミッタ・イネーブル(Transmitter Enable)

SCI のトランスミッタを使用するには、TE を1 にする必要があります。TE = 1なら、SCI はTxD ピンをSCI システムの出力として使用します。

SCI がシングルワイヤ動作に設定されている場合(LOOPS = RSRC = 1)、単独のSCI 通信ライン(TxD ピン)の通信方向はTXDIR で決まります。

TE は、送信の処理中にTE = 0 をライトした後でTE = 1 をライトすると、アイドル・キャラクタのキュー登録にも使用できます。

TE に0 がライトされていれば、データ、キュー内のアイドル・キャラクタ、またはキュー内のブレーク・キャラクタの送信が完了するまではトランスミッタがポートTxD ピンを制御します。その後で、ピンは汎用I/O ピンに戻ります。

0 = トランスミッタはオフ。

1 = トランスミッタはオン。

bit 2[RE]レシーバ・イネーブル(Receiver Enable)

SCI レシーバがオフなら、RxD ピンは汎用ポートI/O ピンに戻ります。LOOPS = 1 の場合、RxD

ピンはRE = 1 であっても汎用I/O ピンに戻ります。

0 レシーバはオフ。

1 レシーバはオン。

bit 1[RWU]レシーバ・ウェイクアップ制御(Receiver Wakeup)

このビットに1 をライトすると、SCI レシーバはスタンバイ状態に移行して、選択されたウェイクアップ条件のハードウェアによる自動検出を待ちます。

ウェイクアップ条件は、メッセージ間のアイドルライン(WAKE = 0 でアイドルライン・ウェイクアップ)またはキャラクタの最上位データ・ビットの論理1 です(WAKE = 1 でアドレスマーク・ウェイクアップ)。

RWU は、アプリケーション・ソフトウェアがセットして、通常は選択されたハードウェア条件により自動的にクリアされます。

0 = SCIレシーバは通常動作。

1 = SCIレシーバはスタンバイ状態でウェイクアップ条件を待機。

bit 0[SBK]ブレークの送信(Send Break)

SBK に1 をライトしてから0 をライトすると、送信データ・ストリームのキューにブレーク・キャラクタが登録されます。

SBK = 1 を維持すれば、10 または11(BRK13 = 1 なら13 または14)ビット・タイムの論理0 からなるブレーク・キャラクタがさらにキューに登録されます。

送信状態とSBK のセットとクリアをするタイミングによっては、ソフトウェアでSBK をクリアする前に2 個目のブレーク・キャラクタがキューに登録されることがあります。

0 トランスミッタは通常動作。

1 送出するブレーク・キャラクタをキューに登録。

【SCIxS1】SCI ステータス・レジスタ1(SCI Status Register 1)

7 6 5 4 3 2 1 0 SCIxS1 TDRE TC RDRF IDLE OR NF FE PF R/W R R R R R R R R RESET 0 0 0 0 0 0 0 0

bit 7[TDRE]送信データ・レジスタ空白フラグ(Transmit Data Register Empty Flag)

TDRE は、リセットの後、および送信データが送信データ・バッファから送信シフタに

転送されてバッファ内に次のキャラクタの空き領域が生じるとセットされます。TDRE をクリアするには、TDRE = 1 のと

きにSCIxS1 をリードしてからSCI データ・レジスタ(SCIxD)にライトします。

0 = 送信データ・レジスタ(バッファ)はフル。

1 = 送信データ・レジスタ(バッファ)は空白。

記述例

/***** 初期設定 *****/

while (SCI1S1_TDRE); // 送信レジスタ空き待ち

SCI1D = TX_BUF; // 送信

bit 6[TC]送信完了フラグ(Transmission Complete Flag)

TC は、リセットの後、およびTDRE = 1 のときに送信中のデータ、プリアンブル、またはブレーク・キャラクタがないときにセットされます。

0 = トランスミッタは処理中(データ、プリアンブル、またはブレークを送信中)。

1 = トランスミッタはアイドル(送信処理は完了)。

TC をクリアするには、TC = 1 のときにSCIxS1 をリードして以下のいずれかの処理を実行します。

○ SCIデータ・レジスタ(SCIxD)に次の送信データをライトする

○ TEを0 から1 に変更してプリアンブルをキューに入れる

○ SCIxC2のSBK に1 をライトしてブレーク・キャラクタをキューに入れる

記述例

/***** 初期設定 *****/

while (SCI1S1_TDRE); // 送信レジスタ空き待ち

SCI1D = TX_BUF; // 送信

while (SCI1S1_TC); // 送信完了待ち

RE = 1; // 受信モードに切り替え

DE = 1; // 受信モードに切り替え

while (SCI1S1_RDRF) // 受信完了待ち

bit 5[RDRF]受信データ・レジスタ・フル・フラグ(Receive Data Register Full Flag)

RDRF は、キャラクタが受信シフタから受信データ・レジスタ(SCIxD)に転送されるとセットされます。

RDRF をクリアするには、RDRF = 1 のときにSCISCIxS1 をリードしてからSCI データ・レジスタ(SCIxD)をリードします。

0 = 受信データ・レジスタは空白。

1 = 受信データ・レジスタはフル。

記述例

/***** 初期設定 *****/

while (SCI1S1_TDRE); // 送信レジスタ空き待ち

SCI1D = TX_BUF; // 送信

while (SCI1S1_TC); // 送信完了待ち

RE = 1; // 受信モードに切り替え

DE = 1; // 受信モードに切り替え

while (SCI1S1_RDRF) // 受信完了待ち

bit 4[IDLE]アイドルライン・フラグ(Idle Line Flag)

IDLE は、処理を終えた後でSCI 受信ラインがフル・キャラクタ・タイムの期間でアイドルになるとセットされます。

ILT = 0 なら、レシーバはスタート・ビットの後からアイドル・ビットのカウントを開始します。

受信キャラクタの全ビットが1 の場合にレシーバがアイドルラインを検出するには、これらのビット・タイムとストップ・ビットを論理High のフル・キャラクタ・タイム(M 制御ビットに応じて10 または11 ビット・タイム)でカウントする必要があります。ILT = 1 なら、レシーバはストップ・ビットの後からアイドル・ビットのカウントを開始します。

そのため、レシーバがアイドルラインを検出する場合に、直前のキャラクタの末尾のストップ・ビットおよび論理High のビット・タイムを、論理High のフル・キャラクタ・タイムとしてカウントしません。

IDLE をクリアするには、IDLE = 1 のときにSCIxS1 をリードしてからSCI データ・レジスタ(SCIxD)をリードします。

一度IDLE がクリアされると、新しいキャラクタの受信でRDRF がセットされるまでは再びセットされることはありません。

受信ラインのアイドル状態が長引く場合でも、IDLE がセットされるのは1 回だけです。

0 = アイドルラインは検出されていない。

1 = アイドルラインが検出された。

bit 3[OR]レシーバ・オーバラン・フラグ(Receiver Overrun Flag)

OR は、新しいシリアル・キャラクタを受信データ・レジスタ(バッファ)に転送する準備が整っている場合に、すでに受信済みのキャラクタがまだSCIxD からリードされていないとセットされます。

このケースでは、新しいキャラクタ(および関連するすべてのエラー情報)はSCIxD に空き領域がないという理由で失われます。

OR をクリアするには、OR = 1 のときにSCIxS1 をリードしてからSCI データ・レジスタ(SCIxD)をリードします。

0 オーバランなし。

1 受信オーバラン(新しいSCI データは失われる)。

bit 2[NF]ノイズ・フラグ(Noise Flag)

レシーバは、高度なサンプリング技法を使用してスタート・ビットで7 回のサンプル、各データ・ビットとストップ・ビットでは各3 回のサンプルを取得します。

フレームのビット・タイム内でこれらのサンプルのいずれかが他のサンプルと一致しない場合に、キャラクタのRDRF フラグがセットされるのと同時にNF フラグがセットされます。

NF をクリアするには、SCIxS1 をリードしてからSCI データ・レジスタ(SCIxD)をリードします。

0 = ノイズは検出されていない。

1 = SCIxDの受信キャラクタでノイズが検出された。

bit 1[FE]フレーミング・エラー・フラグ(Framing Error Flag)

FE は、レシーバがストップ・ビットの位置で論理0 を検出した場合に、RDRF と同時にセットされます。このビットは、レシーバがキャラクタ・フレームを正しく整列できなかった可能性を示します。FE をクリアするには、FE = 1 のときにSCIxS1 をリードしてからSCI データ・レジスタ(SCIxD)をリードします。

0 = フレーミング・エラーは検出されていない。 ただし、フレーミングが正しいことは保証されない。

1 = フレーミング・エラー。

bit 0[PF]パリティ・エラー・フラグ(Parity Error Flag)

PF は、パリティがイネーブル(PE = 1)のときに受信キャラクタのパリティ・ビットと予想されるパリティ値が一致しない場合に、RDRF と同時にセットされます。

PF をクリアするには、SCIxS1 をリードしてからSCI データ・レジスタ(SCIxD)をリードします。

0 = パリティ・エラーなし。

1 = パリティ・エラー。

【SCIxS2】SCI ステータス・レジスタ2(SCI Status Register 2)

7 6 5 4 3 2 1 0 SCIxS2 LBKDIF RXEDGIF --- RXINV RWUID BRK13 LBKDE RAF R/W R/W R/W R R/W R/W R/W R/W R RESET 0 0 0 0 0 0 0 0

bit 7[LBKDIF]LIN ブレーク検出割込みフラグ(LIN Break Detect Interrupt Flag)

LBKDIF は、LIN ブレーク検出回路がイネーブルでLIN ブレーク・キャラクタが検出された場合にセットされます。

LBKDIF は1 をライトするとクリアされます。

0 = LINブレーク・キャラクタは検出されていない。

1 = LINブレーク・キャラクタを検出。

bit 6[RXEDGIF]RxD ピンのアクティブ・エッジ割込みフラグ(RxD Pin Active Edge Interrupt Flag)

このビットをセットすると、受信データ入力の極性が反転します。

0 = 受信データを反転しない。

1 = 受信データを反転。

bit 4[RXINV]受信データの反転(Receive Data Inversion)

このビットをセットすると、受信データ入力の極性が反転します。

0 = 受信データを反転しない。

1 = 受信データを反転。

bit 3[RWUID]受信ウェイクアップのアイドルの検出(ReceiveWake Up Idle Detect)

RWUID は、レシーバをウェイクアップするアイドル・キャラクタでIDLE ビットをセットするかどうかを制御します。

0 = 受信がスタンバイの状態(RWU = 1)で、アイドル・キャラクタの検出時にIDLE ビットをセットしない。

1 = 受信がスタンバイの状態(RWU = 1)で、アイドル・キャラクタの検出時にIDLE ビットをセットする。

bit 2[BRK13]生成するブレーク・キャラクタの長さ(Break Character Generation Length)

BRK13 は、送出するブレーク・キャラクタの長さの選択に使用します。フレーミング・エラーの検出はこのビットによる影響を受けません。

0 = 送出されるブレーク・キャラクタの長さは10 ビット・タイム(M = 1 なら11 ビット・タイム)。

1 = 送出されるブレーク・キャラクタの長さは13 ビット・タイム(M = 1 なら14 ビット・タイム)。

bit 1[LBKDE]LIN ブレーク検出のイネーブル(LIN Break Detection Enable)

LBKDE は、検出するブレーク・キャラクタの長さの選択に使用します。

LBKDE がセットされている間は、フレーミング・エラー(FE)フラグと受信データ・レジスタ・フル(RDRF)フラグはセットされません。

0 = 検出されるブレーク・キャラクタの長さは10 ビット・タイム(M = 1 なら11 ビット・タイム)。

1 = 検出されるブレーク・キャラクタの長さは11 ビット・タイム (M = 1 なら12 ビット・タイム)。

bit 0[RAF]LIN ブレーク検出のイネーブル(Receiver Active Flag)

RAF は、SCI レシーバが有効なスタート・ビットの開始を検出するとセットされ、レシーバがアイドルラインを検出すると自動的にクリアされます。

このステータス・フラグは、MCU をストップ・モードに移行する前に、SCI キャラクタの受信中かどうかを確認するのに使用できます。

0 = SCIレシーバはアイドルでスタート・ビットを待機中。

1 = SCIレシーバは処理中(RxD 入力はアイドルではない)。

【SCIxC3】SCI 制御レジスタ3(SCI Status Register 3)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| SCIxS3 | R8 | T8 | TXDIR | TXINV | ORIE | NEIE | FEIE | PEIE |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| RESET | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

bit 7[R8]レシーバの9 番目のデータ・ビット(Ninth Data Bit for Receiver)

SCI を9 ビット・データに設定していれば(M = 1)、R8 はSCIxD レジスタにあるデータの最上位ビットの左に位置する9 番目の受信データ・ビットと見なされます。

9 ビット・データのリードでは、SCIxD の前にR8 をリードする必要があります。

これは、SCIxD をリードすることで自動フラグ・クリア・シーケンスが完了するために、R8 とSCIxD が新しいデータで上書きされる可能性があるためです。

bit 6[T8]トランスミッタの9 番目のデータ・ビット(Ninth Data Bit for Transmitter)

SCI を9 ビット・データに設定していれば(M = 1)、T8 はSCIxD レジスタにあるデータの最上位ビットの左に位置する9 番目の送信データ・ビットと見なされます。

9 ビット・データのライトでは、SCIxD がライトされた後で9 ビット値の全体がSCI シフト・レジスタに転送されます。

そのため、T8 を前回とは異なる値に変更する場合は、SCIxD の前にT8 にライトする必要があります。

T8 を新しい値に変更する必要がなければ(マークの生成やパリティにスペースを設定する場合など)、SCIxD のライトのたびにT8 にライトする必要はありません。

bit 5[TXDIR]シングルワイヤ・モードでのTxD ピンのデータ方向(TxD Pin Direction in Single-Wire Mode)

このビットは、SCI をシングルワイヤの半二重動作に設定している

場合に(LOOPS = RSRC = 1)、TxD ピンのデータ方向を決定します。

0 = TxDピンは、シングルワイヤ・モードでは入力。

1 = TxDピンは、シングルワイヤ・モードでは出力。

bit 4[TXINV]送信データの反転(Transmit Data Inversion)

このビットをセットすると、送信データ出力の極性が反転します。

0 = 送信データを反転しない。

1 = 送信データを反転。

bit 3[ORIE]オーバラン割込みイネーブル(Overrun Interrupt Enable)

このビットは、ハードウェア割込み要求を生成するオーバラン・フラグ(OR)をイネーブルにします。

0 = OR割込みはディセーブル(ポーリングを使用)。

1 = OR=1ならハードウェア割込みが要求される。

bit 2[NEIE]ノイズ・エラー割込みイネーブル(Noise Error Interrupt Enable)

このビットは、ハードウェア割込み要求を生成するノイズ・フラグ(NF)をイネーブルにします。

0 = NF割込みはディセーブル(ポーリングを使用)。

1 = NF=1ならハードウェア割込みが要求される。

bit 1[FEIE]フレーミング・エラー割込みイネーブル(Framing Error Interrupt Enable)

このビットは、ハードウェア割込み要求を生成するフレーミング・エラー・フラグ(FE)をイネーブルにします。

0 = FE割込みはディセーブル(ポーリングを使用)。

1 = FE=1ならハードウェア割込みが要求される。

bit 0[PEIE]パリティ・エラー割込みイネーブル(Parity Error Interrupt Enable)

このビットは、ハードウェア割込み要求を生成するパリティ・エラー・フラグ(PF)

をイネーブルにします。

0 = PF割込みはディセーブル(ポーリングを使用)。

1 = PF=1ならハードウェア割込みが要求される。

【SCIxD】SCI データ・レジスタ(SCI Data Register)

7 6 5 4 3 2 1 0 SCIxD R7/T7 R6/T6 R5/T5 R4/T4 R3/T3 R2/T2 R1/T1 R0/T0 R R7 R6 R5 R4 R3 R2 R1 R0 W T7 T6 T5 T4 T3 T2 T1 T0 RESET 0 0 0 0 0 0 0 0

このレジスタは、実際には2 つの部分に分かれています。リードを行うとリード専用の受信データ・バッファの内容が返され、ライトを行うとライト専用の送信データ・バッファがライトされます。このレジスタにデータを代入すると、設定されたシリアル送信が開始されます。

また、受信信号があれば自動的に受信し、RDRFが1となります。このRDRFが1であることを確認してから、SCIxDを読込むと正しい受信データを受け取る事が出来ます。

このレジスタのリードおよびライトは、SCI ステータス・フラグの自動フラグ・クリア・メカニズムにも組み込まれています。

記述例

/***** 初期設定 *****/

while (SCI1S1_TDRE); // 送信レジスタ空き待ち

SCI1D = TX_BUF; // 送信

while (SCI1S1_TC); // 送信完了待ち

RE = 1; // 受信モードに切り替え

DE = 1; // 受信モードに切り替え

while (SCI1S1_RDRF) // 受信完了待ち

RX_BUF = SCI1D; // 受信