1.はじめに

2002年の夏ごろ、CQ出版のVHDLで学ぶCPLD学習セット(ALTERA社のMAX9000Sシリーズを使うやつです)を購入したのですが、いろいろあって、ほったらかしにしていました。そして、今年の5月あたりに、学習をはじめようとしたところ、無料で使えたleonard spectrum(Alteraバージョン)が使えないという事態になっていることに気がつきました。せっかく買った学習セットがパー!

そんなこんなで、VHDLの勉強ができなくなってしまったと嘆いていたのですが、同Alteraが提供している、Quartus 2 Web Editionを使えば、VHDLが使用できることがわかり、早速試してみました。私のOS環境が、Windows98なので、Quartus2 Web Edition Ver2.2を使用します。最新バージョンの3.0は、Win98非対応なので。

ここでは、VHDLの説明とか、開発ソフトの詳しい使い方とか、そういうものは載せていません(いろいろ勉強しながら、別の機会にしたいと思います。いずれは、文中にあるVHDLソースを実際にダウンロードするためには、ハード的にどうすればいいとか、そのあたりまでちゃんと書きたいのですが)。まずは、Quartusというソフトを使って、入手の容易なMAX3000シリーズを使ってみましたよ、という簡単なレポートにとどめます。このレポートで、MAX3000+Quartusの組み合わせでVHDLを使って遊べるということがわかってもらえればと思います。

2.素子を探す

Quartus2 web editionは、5V系のMAX7000S非対応のため、3.3V系のMAX7000AやMAX700AE,2.5V系のMAX7000Bを使用しなければなりません。ところが、秋葉原でMAX7000AEやBが入手できず(MAX7000Sしかない)店先で悩んでいたところ、MAX7000Sの隣に、MAX3000Aシリーズが置いてありました。店をでて、インターネットカフェに入り、MAX3000シリーズについて調べてみると、これはMAX7000シリーズのからちょっとだけ機能を削ったものみたいなので、用途的には十分なものであることと、Quartus2 Web Editionがこの素子に対応していることがわかり、再びお店にいき、MAX3000A(EPM3032ALC44-10)を購入しました。ちなみに、購入した店は、若松通商です。

残念ながら、若松通称では、MAX3000シリーズをおかなくなってしまいました。(2004年/4月)

3.Quartus2 web editionを使う。

私のネット環境は、アナログ回線なので、ファイル容量の大きいQuartus2 Web Editionをダウンロードすることは不可能に近いため、ADSL環境をもつ兄貴に頼んでダウンロードしてもらいました。このソフトは無料では有りますが、使用にはライセンス申請が必要なので、ライセンス手続き(簡単です)を行います。こうして、Quartus2 Web Editionがつかえるようになりました。

まずは、非常に簡単なVHDLファイルを作って、試してみることにしました。

3-1.新規プロジェクトの作成

Quartus2 Web Editionを起動し、Fileメニューから新規プロジェクトを選択します。すると、プロジェクトウィザードが起動し、「New Project Wizard: Directory,Name,and Top-level Entity」というウィンドウが開きます。

この画面で、上段に作業用ディレクトリを、中段にプロジェクト名を、下段に最上位エンティティの名前を入れます。プロジェクト名を入力すると、最上位エンティティ名の項目にはプロジェクト名と同じ名称が自動で入力されます。

とりあえず、

作業用ディレクトリ D:\0_Data\f_VHDL\test4\

プロジェクト名 test4

最上位エンティティ名 test4

としました。

Nextを押して、2ページ目、3ページ目はスキップし、4ページ目のDevice Familyの選択にて、MAX3000Aを選びます。ここで、MAX3000Aシリーズのなかで、何を使うかが決まっているのなら、Do you want to assign a specific device? を yes にしておきます。

私は、すでにEPM3032AALC44-10を購入してあるので、yesを選択しました。

Nextを押して、Select a target Device のページに移り、EPM3032ALC44-10を選択します。

Nextを押すと、最終確認としていままで選択した一覧が出てきますから、ここで確認をしてFinishを押します。

3-2 VHDLファイルの作成

とりあえず、作成する回路は、図2のような簡単なものとします。これをVHDLで記述すると、図1のようになります。この図1は、以下の操作でQuartus2のテキストエディタを起動して、その中に記述します。

1) File Newを選択して、Device Design Filesタブの中の、VHDLファイルを選択して OKを押します。

2) すると、Vhdl1.vhdというファイル名で、テキストエディタが起動しますので、このエディタで

図2のVHDLソースを記述します。

3) ソースの記述が終わったら、File のSave as..で、Test4.vhdというファイル名で保存します。

library ieee;

use ieee.std_logic_1164.all;

entity TEST4 is

port(POUT: ou std_logic;

PIN : in std_logic);

end TEST4;

architecture RTL of TEST4 is

begin

POUT <= PIN;

end RTL;

図1 とりあえず作ってみた簡単なVHDLファイル

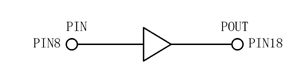

VHDL上では、PIN端子の入力をそのままPOUT渡す回路をあらわしていますが、実際の回路では直結にならず、間にバッファが入ります。

図2 図1のVHDLを図記号化するとこうなる

3-3 VHDLファイルのコンパイル

Processing の中の Start Compilationを選択し、コンパイルを行います。無事終了すると、Full Compilation was successfulと表示されたwindowが開きますから、OKを押します。

3-4 ピン配置

EPM3032Aのどのピンに、どの信号を割り当てるのかを決定します。図1の回路で、必要なピンはPINとPOUTです。とりあえず、PINを8ピンに、POUTを18ピンに割り当ててみます。

1) Assinmentsの中の、Assignment Editorを選択し、Assignment Editorを起動します。

2) Source Nameのセルに書かれている<<New>>をダブルクリックすると、セルが空欄となり、

セル右側に三角マークがでてきますので、その三角マークを押し、Node Filderを選択します。

3) Node Finderのウィンドウが開くので、Named欄は*,FilterはPins:allに設定して、Start

ボタンを押し、VHDLに記述されている入出力ピンの一覧を検索させます。

4) すると、Nodes Found欄に、PINとPOUTが出てきますから、まずはPINを選択して、>

ボタンを押して、Selected NodesにPINを表示させます。

5) ここで、OKボタンをおして、Node Finderウインドウを閉じると、Assinment Editorの

Source Name には、選択したPINが表示されています。

6) 次に、このPINを選択した状態で、Assinmentsメニューの中のAssinments Pinを選択し

ます。すると、何やらメッセージがだらだらかかれたウィンドウが二回でますが、無視

してOKを押していくと、Assign Pinsのウィンドウが開きます。

PINを8ピンに設定してみましょう。

7) まずAvailable Pins & Exsisting Assignmentsの一覧で、Number列の8を選択します。

8) 次に、AssignmentのPin Name項目の、...ボタンを押します。

9) すると、再びNodeFinderウィンドウが開きますから、先ほどと同じように、Startボタン

を押した後、PINを選択し、>ボタンを押してSelect Nodes欄にPINを移し、OKボタンを押します。

10) これで、Assign PinsのPin name 欄に、PINが記入されましたから、Addボタンを押し

て、8ピンをPINに割り当てます。

11) OKを押してウィンドウを閉じます。このとき、またいろんなメッセージの書かれたウィンド

ウが2度ほどでてきますが、無視してOKを押しつづけると、Assignment Editorのウィンド

ウに戻り、ValueにPin_8がはいってます 。

12) 同じように、POUTを18ピンに割り当てます。

3-5 コンパイル

ピン配置が終了したら、再びProccenssingメニューのRun Compirationを線tなくして、コンパイルを行います。

3-6 ダウンロード

作成した回路を、EPM3032ALC44-10に書きこみます。書き込みには、ダウンロードケーブルが必要です。ダウンロードケーブルは市販もされていますが、回路が簡単なので、自作したほうが安く済みます。回路は、ALTELAのサイト、もしくはVHDL関連の本や、ALTERAのCPLDについて特集している雑誌などに掲載されていますので、そちらを参考にされるとよいと思います。

1) ToolsメニューのProgrammerを選択します。

2) Programming Hardwareが、ByteBlasterMV[LPT1]になっていることを確認します。もしなって

いなかったら、Setupボタンを押して、ByteBlasterMVを選択します。

3) Add Fileを選択し、コンパイルで作成された、test4.pofを選択します。

4) Program/Configureにチェックして、startボタンを押します。

これで、終了です。

ほんとは、書きこみ前にシミュレーションを行い、動作確認をするのですが、シミュレーションのやりかたまで記述する元気がなかったので、省略しました。

そもそも、CPLD関連は、雑誌などに詳しく出ているので、そちらを見るのが一番かと思います。

こうして、VHDLを使う環境が出来あがりました。これで、いままで、74シリーズのロジックICを駆使して作成していたデジタル回路が、わずか一つの素子で済ましてしまうことが出来るようになったわけです。これから、いろいろVHDLで遊んでみたいと思います。

参考文献

Desing wave magazign 2003年1月号 3月号 10月号 CQ出版社

FPGA/PLD設計スタートアップ CQ出版社