OTA偲偼 Operational Trans conductance Amplifier偺棯偱擖椡怣崋偑揹埑側偺偵懳偟偰弌椡怣崋偼揹棳(掕揹棳弌椡)偱偁傞傾儞僾偱偦偺僐儞僟僋僞儞僗(弌椡揹棳/擖椡揹埑)傪壜曄偱偒傞傾儞僾偱偡丅丂偦偺愄偼 TCA側偳偲傕屇偽傟偰偄傑偟偨丅 乮Trans conductance Amplifier乯丂捠忢偼婣娨傪偐偗側偄偱巊梡偟傑偡偑VCR偲偟偰偺巊梡丄偡側傢偪VCF偺1慺巕偲偟偰偺巊梡側偳偱偼婣娨傪偐偗傑偡丅(*0乯

偄傠偄傠側峔憿偺OTA偑懚嵼偡傞偲巚偄傑偡偑桳柤側傕偺偵偼 CA3080, CA3280, LM13600, 13700, BA6110側偳偑偁傝傑偡丅丂偙偺拞偱 3080, 13600,13700偼婎杮揑晹暘偑傎傏摨偠傛偆側峔憿傪偟偰偄傑偡丅丂3280偼峔憿偑堎側傝丄BA6110偼偙偺3280偺峔憿傪柾偟偨傕偺(*1)偲側偭偰偄傞傛偆偱偡丅

| OTA偼analog synth偵偍偄偰廳梫側 Key device偱偡丅丂OTA偑側偔偲傕analog synth偼峔惉偱偒傑偡偑analog synth偺敪揥偵偼側偔偰偼側傜側偄device偱偟偨丅丂SSM/CEM偺IC傕VCA/VCF chip偼OTA傪拞怱偲偟偰峔惉偝傟偰偄傞偱偟傚偆偟嵎摦夞楬峔惉偺VCA偼OTA偺尨揰偨傞傕偺偱偡偟丄堦尒OTA偲偼堎側傞傛偆側 diode ring傕摦嶌偼 OTA偲崜帡偟偰偄傑偡丅丂側偵傛傝 analog synth偼丂voltage control偱摦嶌偡傞揹巕夞楬側偺偱偡偐傜偦傟傪暯堈偵幚尰偡傞堊偵偼側偔偰偼側傜側偄傕偺偱偡 |

丂*0: 掕揹棳弌椡偱偼偙傑傞応崌丅---> OTA偺VCR愙懕

丂*1: 彮側偔偲傕撪晹摍壙夞楬偺僽儘僢僋恾儗儀儖偱偼OTA晹暘偼摨偠峔惉偱偡丅

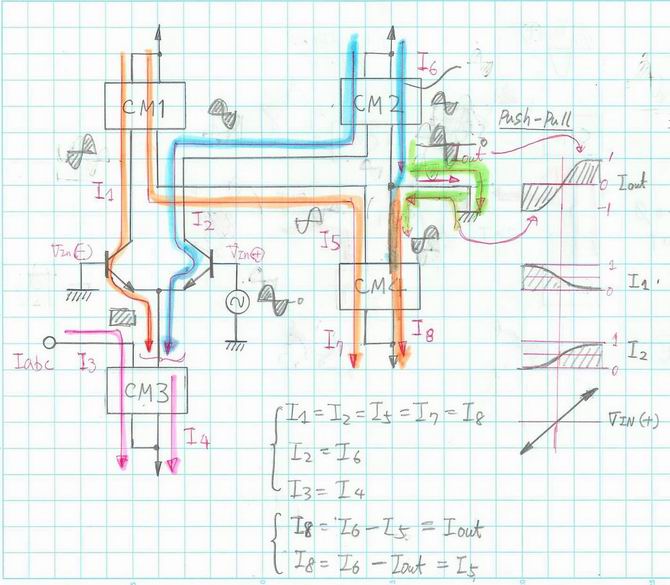

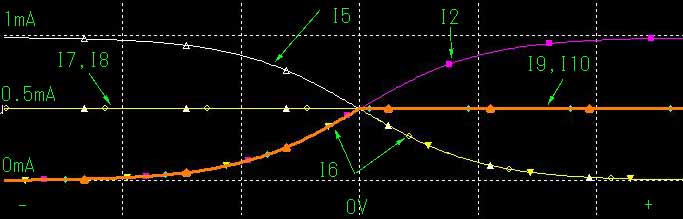

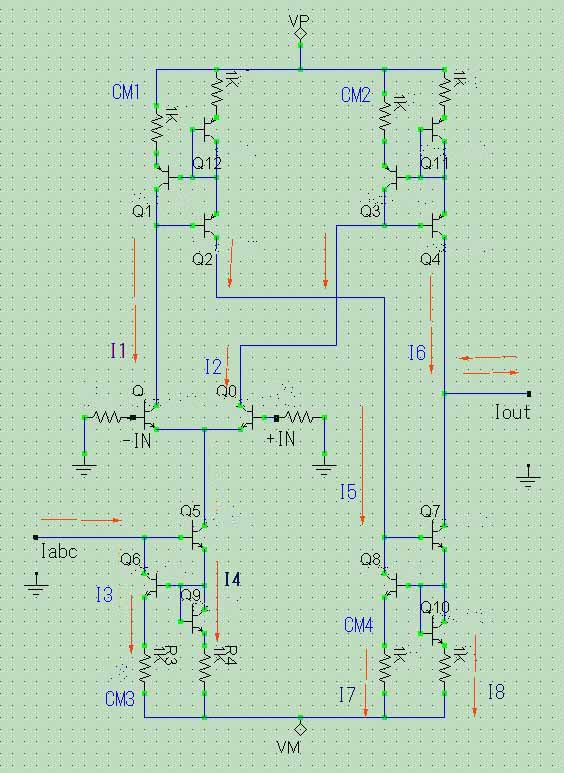

忋恾偵 3080丄13600 僞僀僾偺 OTA儌僨儖傪帵偟傑偡丅丂

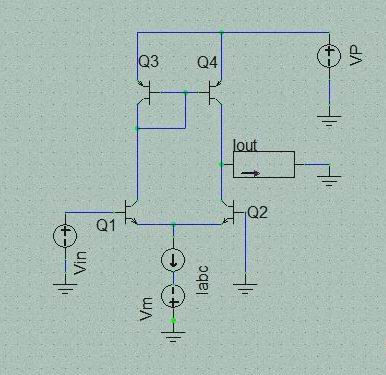

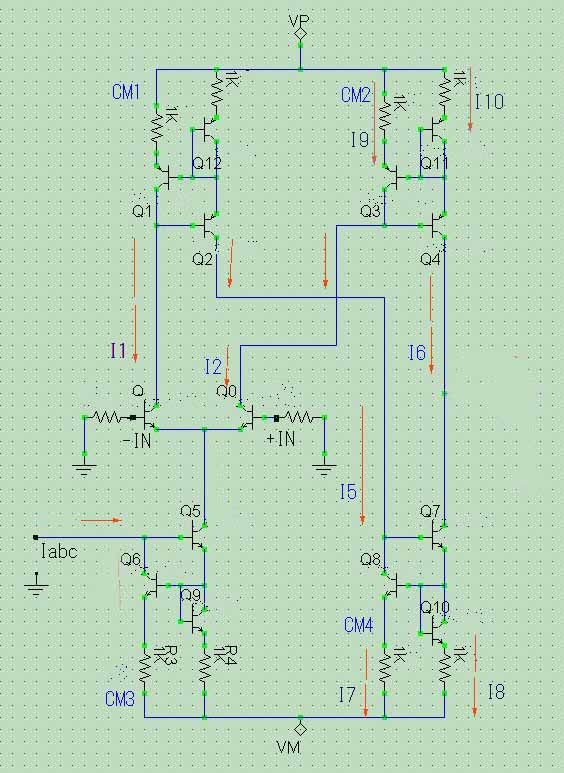

4屄偺僇儗儞僩儈儔乕偲 1慻偺嵎摦夞楬偱峔惉偝傟偰偍傝婎杮揑偵偼gm壜曄曽幃偺analog 忔嶼婍偱偡丅丂擖弌椡抂巕偼 +,-偺嵎摦揹埑怣崋擖椡偲 惂屼揹棳擖椡 Iabc丄揹棳弌椡抂巕丄+,-揹尮抂巕偱峔惉偝傟傑偡丅

* 忋恾偱嵎摦夞楬偺嵍懁偺iniput偑 (-) 抂巕偱偁傞偙偲偵拲堄丅

|

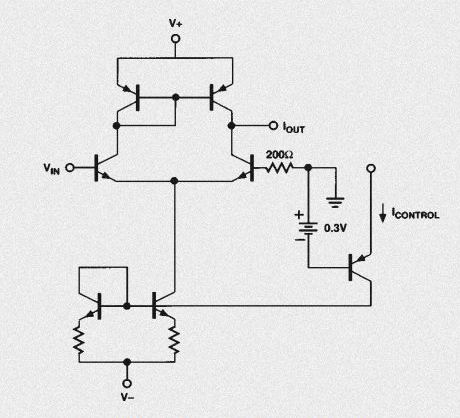

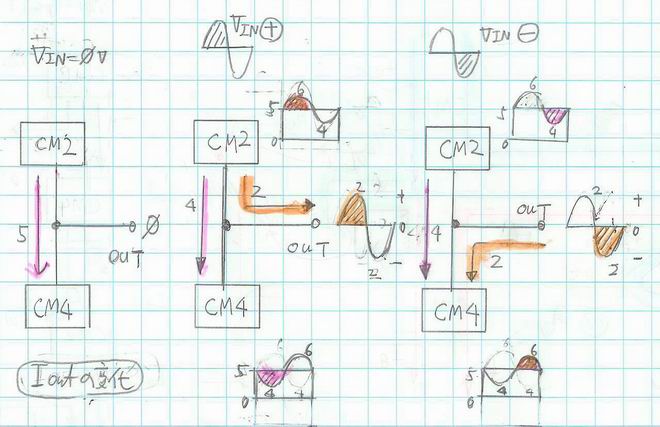

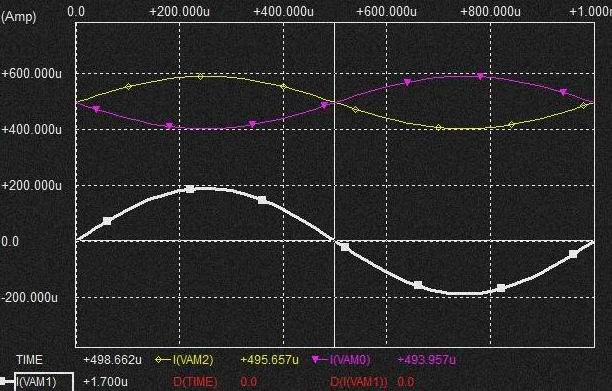

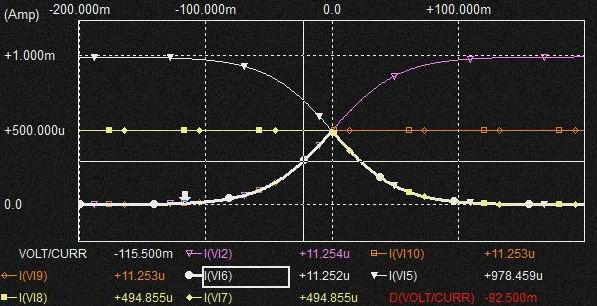

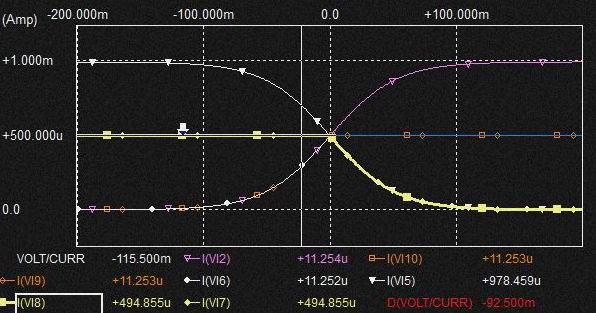

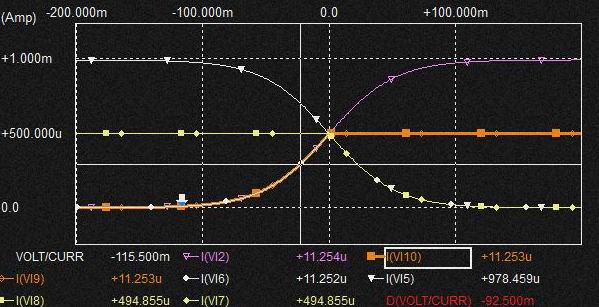

嵎摦夞楬偺揹棳娭學偼掕揹棳尮偺I4偵傛偭偰巟攝偝傟傑偡偑丄偙偺I4偼僇儗儞僩儈儔乕 CM3偐傜摼傜傟傞掕揹棳尮側偺偱奜晹揹棳Iabc偵傛傝巟攝偝傟傑偡丅丂嵎摦夞楬偺晧壸偑CM1偲CM2側偺偱偦傟偧傟偺僇儗儞僩儈乕儔乕偵偮偄偰偼嵎摦夞楬偵棳傟傞揹棳懁偺I1丆I2偑巟攝揑偱偦偺僐僺乕揹棳偑偦傟偧傟I5偲I6偱偦傟偧傟偑僇儗儞僩儈儔乕CM4偵報壛偝傟傑偡丅丂CM4偵偮偄偰偼I5偑巟攝揑側偺偱I8偼昁慠揑偵I5偲摨偠曄壔偵側傜側偗傟偽側傝傑偣傫丅 偟偐偟弌椡偵壗傕偮側偑側偗傟偽偙傟偑幚尰偱偒傑偣傫丅丂弌椡偵壗偐偮側偘偽(偨偲偊偽GND偵乯偦偙偐傜I6偩偗偱偼晄懌暘偺揹棳傪庢傝崬傒丄懡偗傟偽弌椡偵嵎暘傪攔弌偡傞偙偲偱I5=I7=I8傪幚尰偟out put偺揹棳曄壔偲偟偰偼掕揹棳偺push/pull摦嶌傪峴偆偙偲偵側傝偦傟偑擖椡揹埑(IN)偵懳偡傞弌椡揹棳偲側傝傑偡丅丂偙偺摦嶌偵傛偭偰僇儗儞僩儈儔乕偺椉懁偺揹棳曄壔偼摨偠偵側傝僇儗儞僩儈儔乕偲偟偰惓忢摦嶌偲側傝傑偡(*1)丅丂摉慠偺偙偲側偑傜偙偺弌椡揹棳偺戝偒偝偺尦(gm)偼Iabc偺抣傪斀塮偟偨傕偺偵側傝傑偡丅丂掕揹棳尮偺晄巚媍傪棙梡偟偨摦嶌偱偡偹丅(*2) 弌椡嬤偔偺僇儗儞僩儈儔乕CM4偵偍偄偰I2 + - (I1) 偲偄偆 嵎摦憹暆儀乕僗偺VCA偵偍偗傞屻抜偺OP AMP偵傛傞嵎摦AMP偺戙傢傝偺摦嶌傪偝偣偰偄傞傢偗偱偡丅乮偙偺応崌揹埑偱側偔偰掕揹棳弌椡偱偡偑乯

*1: 弌椡偵壗傕愙懕偟側偔偰傕幚偼僇儗儞僩儈儔乕偲偟偰偼椉懁偺揹棳偼摨偠曄壔偵側傞丅

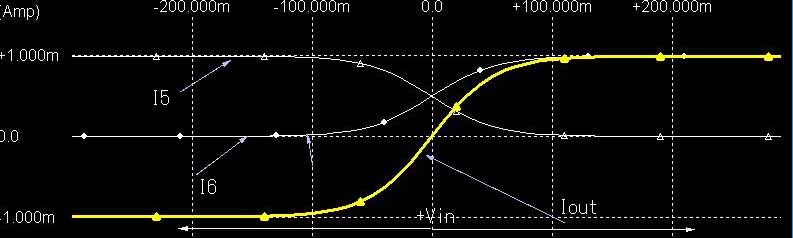

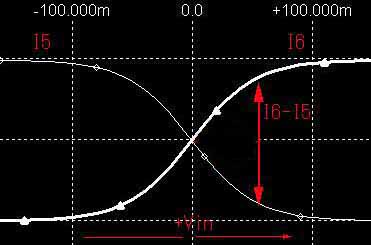

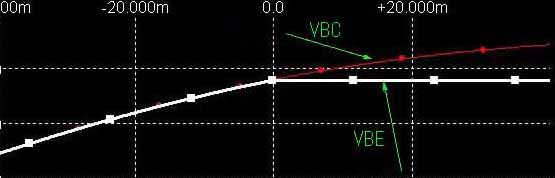

傛傝扨弮側峔憿偺OTA偲偟偰偼埲壓偺傛偆側夞楬偵側傝傑偡丅丂婎杮摦嶌尨棟偼忋婰偲摨條偱偡丅 丂偙偺応崌偼嵍懁偺Vin偑Vin偑僾儔僗憹壛偱Iout偼攔弌(+Iout)丄Vin儅僀僫僗尭彮偱Iout偼媧偄崬傒(-Iout)偵側傝傑偡丅丂SSM2040 VCF偺 core晹暘傕偙傟偵弨偠偨峔惉偺傛偆偱偡偑丅丂偙偺夞楬偵偍偄偰偼惂屼揹棳偺曄壔偵懳偡傞Iout偺捈慄惈偑惂屼揹棳偺忋徃偲偲傕偵埆偔側傞偲偐偄偔偮偐偺寚揰偑偁傞偨傔偦傟傪夝徚偡傞宍偱巒傔偵偁偘偨OTA儌僨儖偼偱偒偰偄傑偡丅 偲偄偆偙偲偼SSM2040側偳偼偙偺寚揰偺塭嬁傪庴偗傞傢偗偱偡偑偦傟偑枴偵側偭偰昡壙偝傟偰偄傞偺偱偟傚偆偐丅丂

忋恾偵偍偄偰Master偲側傞偺偼Iabc偱揹棳抣屌掕偺掕揹棳尮丅傛偭偰僇儗儞僩儈儔乕Q3/Q4偲嵎摦懳Q1/Q2偵偍偄偰Q3偲Q4偺Tr.偺Ic3,IC4偼報壛Audio怣崋偵懳偟偰摨偠摦偒傪偟側偗傟側傜偢丄堦曽Q1偲Q2偺IC1偲Ic2偼媡曽岦偺摦偒傪偡傞昁慠偑偁傞丅傑偨Ic1偲IC3偼摨偠摦偒傪偟側偗傟偽側傜側偄偲偄偆昁慠偑偁傞丅AUDIO怣崋偑0偺帪偼Ic1/Ic2/Ic3/I04偼慡偰摨偠抣偱偡偑Audio怣崋偑僾儔僗傗儅僀僫僗偵側偭偨帪傕巒傔偵彂偄偨忦審偑側傝偨偮堊偵偼奜晹晧壸偵棳傟傞揹棳偑Push-Pull摦嶌傪偟偰IC1偺2攞偺曄壔偺掕揹棳偵側偭偰偮偠偮傑偑崌偆傢偗偱偡丅屌掕偺揹棳尮Iabc傪奜晹揹埑偱曄壔偝偣傟偽OTA偲側傞丅

|

* OTA偵娭偡傞暥專偼奀奜偺嶨帍摍偺傾乕僇僀僽傗崙撪偺彂愋偵傕偄偔偮偐偁傝傑偡丅

* 崙撪

丂1:揹巕揥朷(1976?)

丂2:揹攇壢妛(僄儗僋僩儘僯僋僗儔僀僼)(198?)

丂3:傾僫儘僌IC偺婡擻夞楬愝寁擖栧丂(惵栘塸旻) 4type偺OTA

丂4:傾僫儘僌夞楬偺愝寁丒惢嶌丂(惵栘塸旻) 13600

丂5:僩儔媄(1994/02) 13700

丂6:僩儔媄(1997/10) 13700

* 奀奜

丂01:Musical Engineer's Handbook CA3080

丂02:Electro Music Circuit CA3080/CA3280/13600

丂03:Elektor Electronics(1975/09) CA3080

丂04:Elektor Electronics(1982/04) 13600

丂05:Elektor Electronics(1982/07/08) 13600

丂06:ETI (1988/01) 13700

丂07:Electronic Design(1976/09) discrete

丂08:Nutes & Bolts (2003/04/05) 13700

丂09:RADIO-ELECTRONICS(1988/05/07) CA3080

丂10:Mapllin (1989/06/07) 13700

丂11:Polyphony 1980(01/02) CA3280

丂12:ETI CA3080 curcuit (1979/04)

丂13:Studio Sound ..VCAs (1989/06..09)

偦偺懠

丂奺儊乕僇乕偺 DATA Sheet摍

丂RCA Linear IC App.丂ICAN-677

崙撪曇偺3:偑偲偰傕徻偟偄偲巚偄傑偡偟OTA偵尷傜偢僇儗儞僩儈儔乕丄嵎摦夞楬丄僶儞僪僊儍僢僾揹棳尮摍丄analog婡擻夞楬偺夝愢偲偟偰偼偙偺杮偼堦斣徻偟偄傛偆偵巚偊傑偡丅丂傑偨偙偺杮偺挊幰偑嶲峫暥專偵偁偘偰偄傞"傾僫儘僌廤愊夞楬愝寁媄弍(忋)"傕偲偰傕桳柤側杮偩偲巚偄傑偡丅傑偨13:偼CA3080偺懠偵Pro AUDIO梡偺DBX摍偺Comp.摍偺VCA夞楬偑懡悢宖嵹偝傟偰偄傑偡丅

徻嵶偼忋婰偺暥專傪嶲峫偵偡傟偽偄偄偲巚偄傑偡丅丂婎杮揑側摦嶌尨棟偼忋婰偵帵偟偨傕偺偱偡偑丄埲壓偵嬶懱椺偲寁嶼幃摍傪帵偟偰偍偒傑偡丅