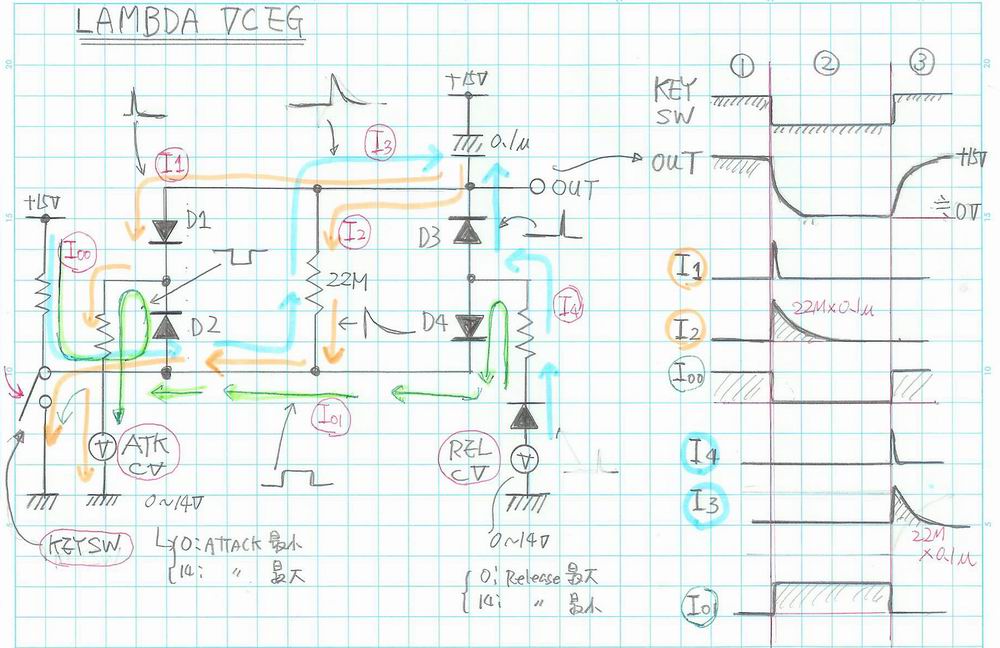

Lambda VCEG

慡尞敪怳壒尮偵偍偗傞EG

Lambda偵尷傜偢慡尞POLY偺壒尮偺奺Key撈棫偺EG偼1偭偺VR偱慡晹偺EG偺Time傪壜曄偡傞娭學偐傜摉慠偺偙偲側偑傜揹埑惂屼偵側偭偰偄傞昁梫偑偁傝傑偡丅丂偨偩PS3000僔儕乕僘偺傛偆側姰慡側poly synth偱偼側偄偺偱娙堈僞僀僾偺揹埑惂屼壔偑側偝傟偰偍傝偨偄傊傫僩儕僢僉乕側夞楬偵側偭偰偄偰柺敀偄偱偡丅

偙偙偱偼lambda偺娙堈揹埑惂屼EG傪徯夘偟偰傒傞偙偲偵偟傑偡丅

丒 LAMBDA偺奺Key偛偲偵憰旛偝傟偰偄傞AR type偺VCEG

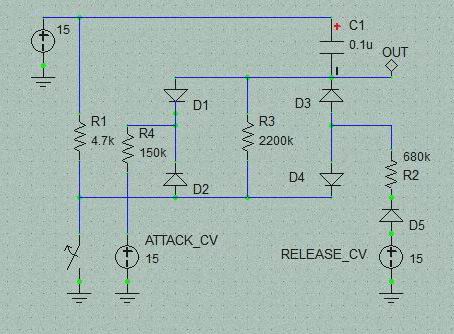

Attack CV / Release CV偺戝偒偝偵傛偭偰time偑曄傢傝傑偡丅attack偼 CV偑彫偝偄傎偳 time偼憗偔 release偼媡偱偡丅忋婰偺夞楬傪尒偰傕偳偆偟偰VCEG偲偟偰婡擻偡傞偺偐丄崻杮揑側敪憐偺旘桇傪棟夝偟側偄偲捈姶揑偵偼側偐側偐棟夝偱偒傑偣傫丅丂偦傟偵偟偰傕傢偢偐10屄埲壓偺晹昳偱1尞暘偺 A/R VCEG偑偱偒偰偟傑偭偰偄傑偡丅偙傟側傜LOW COST偵弌棃傑偡丅

奺Diode偺旝暘掞峈偺曄壔偑attack/release Time偵嶌梡偡傞偺偐偲峫偊傑偟偨偑敿暘惓夝丄敿暘晄惓夝偲偄偆偐杮幙揑偱偼側偄傛偆偱偡丅 Diode偼扨偵SW偲偟偰傕摦偄偰偄傞傛偆偱偡偑偦偆偱偁傟偽偳偆偟偰CR偺帪掕悢夞楬偺抣偑曄壔偱偒傞偺偐丠丅丂幚嵺偼偐側傝僩儕僢僉乕側夞楬摦嶌偲側傝傑偡丅堦弖丄宍偑KORG偺摼堄側diode ring偐偲嶖妎偟傑偡偑偦偆偱偼偁傝傑偣傫丅埲壓偺揹棳/揹埑曄壔偺徻嵶恾傪帵偟傑偡丅

KEY OFF帪丄0.1uF偺 Cap.偼枹廩揹側偺偱(*0)丂OutPut偼+15V丅 Key ON偡傞偲Attack CV偺戝偒偝偵傛偭偰Cap.偑0V偵岦偐偭偰廩揹偝傟偰峴偔偺偱Out Put揹埑偼掅壓偟偰Key ON帪偼CR夞楬偺曅曽偺抂巕偼GND側偺偱0V乮嬤偔乯偵側傟偽attack廔椆丅 Key OFF偵側傟偽 release CV偺戝偒偝偵傛偭偰Cap.偑曻揹偝傟偰峴偒OutPut偑+15V偵側傞偲release time廔椆丅

忋婰偺愢柧偱偼Attack / Release Time偑 Voltage Controll偝傟偰偄傞偙偲偑傢偐傝傑偣傫偺偱奺揹棳偺曄壔傪峫偊偰尒傑偡丅丂Key ON/OFF偵偍偗傞揹棳曄壔偼忋婰偺傛偆偵側傝傑偡丅(OUT put偺傒揹埑曄壔)

*0:

摦嶌忋D2偑柍偔偰傕惉傝棫偪偦偆偱偡偑丄D2偑柍偄偲Cap.偑彮偟廩揹偟偰偟傑偄Key OFF帪 +15V傪曐偰側偔側傝傑偡丅偙偺D2偵傛偭偰Key OFF帪枹廩揹 = +15V偵側傝傑偡丅

KEY OFF帪(relase廔椆屻):

D2偑ON偟偰偄偰I00偺傒偑棳傟偰偄傑偡丅偨偩偟Attack CV 偑 MAX(栺14.4V)帪晅嬤偵側偭偰偄傟偽D2偼OFF (*2)

I1丄I2丄I3丄I01偲I4偼偦傟偧傟0丅

*2:

偡側傢偪 D2偺ON/OFF偑堄枴偑偁傞偺偱偼側偔Key OFF帪丄D2偺僇僜乕僪偑+14V埲忋偺崅揹埵偵側傞傛偆偵I00偼棳傟偰偄傞丅

偙偺D2偑柍偄偲KEYOFF帪out put偺+15V傪曐偰側偔側傞丅

KEY ON帪:

D2偺傾僲乕僪揹埵偑GND儗儀儖偵側傞偺偱堦弖I1偑僷儖僗忬偵棳傟傞丅 偡側傢偪D1偑ON偡傞偲D1傪捠偟偰揹棳偑棳傟偦傟偱

0.1uF偺 Cap.偑廩揹偝傟傞偨傔Out Put偺掅壓傪庴偗偡偖偵OFF丅丂D1偺僇僜乕僪揹埑偑弖帪偵Attack CV儗儀儖偵側偭偨屻偵D1偑OFF偟廩揹宱楬0.1uF偲22M偺宱楬偱棳傟傞I2偺傒偲側傝OutPut偑GND儗儀儖嬤偔偵側傞傑偱懕偔丅

D2偼傾僲乕僪GND側偺偱OFF丅

release CV偑彫偝偄偲偒埲奜偼D4偑ON(*3)偱I01偑棳傟丄D4傾僲乕僪< OUT PUT帪 D3 OFF丅

Out Put偑0V嬤偔偵側傞偲D3偺媡僶僀傾僗偑夝偗傞偔傜偄偱output偼僶儔儞僗偟偰0V嬤偔偱屌掕

I1,I2,I00,I4,I3偼0

*3:

偙偺応崌傕D4偺ON/OFF偑堄枴偑偁傞傢偗偱偼側偔D4偺傾僲乕僪偑0V偐傜0.6V掱搙偺揹埵偵側偭偰D3偑OFF偡傞傛偆偵I01偑棳傟偰偄傞丅

嵞搙KEY OFF帪:

D4偺僇僜乕僪揹埑偑忋偑傝D4偑OFF偡傞偺偱release CV偑D3偺傾僲乕僪偵揱傢傝I4偑僷儖僗忬偵抁帪娫棳傟傞丅(*4)

巒傔 Out Put偼0V偵嬤偄偺偱D3偼媫寖偵ON偡傞偑I4偵傛傝媫懍曻揹偝傟傞偨傔偠偒偵Out Put偑忋徃偟(D3 ON --> OFF)偲側傞丅

*4:

release CV偑0偲偐彫偝偄応崌丄Key OFF傪庴偗偰D4偺僇僜乕僪偑+15V傑偱媫忋徃偡傞巒傔偺堦弖D4偺傾僲乕僪偼0.6V掱搙偵偼偁偑傞偺偱偙偺応崌傕堦弖揹棳偼棳傟Cap.傪曻揹偡傞偺偱堦弖偱D3偼OFF偟丄out Put揹埑傕0.6V掱搙偵偼側傞丅

D2 ON側偺偱I00偑嵞傃棳傟傞丅

0.1uF Cap.偵棳傟傞宱楬偲偟偰偺D3偼OFF偵側傞偺偱Cap.傪曻揹偡傞宱楬偼埲屻I3偑22M偲Cap.偺帪掕悢偱棳傟傞丅

忋恾偐傜attack / release Time偵娭梌偟偰偄傞梫慺偼婎杮22M偺掞峈偲 0.1uF偺capacitor偩偗偲偄偆偙偲偑傢偐傝傑偡丅偡側傢偪婎杮揑側attack/release time偺帪掕悢偼側傫偲屌掕側偺偱偡丅偱偼側偤偦傟偧傟偺time偑壜曄偱偒傞偺偱偟傚偆偐丅

attck CV=0V帪偺椺:丄

CR偺廩曻揹偵diode偺旝暘掞峈偑帪掕悢偲偟偰嶌梡偡傞偺偼 KEY ON捈屻D1偑ON偟偰cap.偺揹壸偑 D1 --R -- Attack CV偵棳傟傞堦弖帪偩偗偱偦傟偵敽偭偰 Cap.偺揹埵(output)媫掅壓偟偰 attack CV揹埑嬤偔偵側傟偽 D1偑OFF偟偰偦偺帪揰偱偺OUT PUT偺揹埵偼偍偍傓偹 attck CV偺抣丅(*1)

偦傟埲崀偼偦偺揹埵偐傜 22M偺掞峈偲 cap.偺帪掕悢偱僇乕僽偑偒傑傞丅( KEY ON捈屻偐傜 22M 偲 Cap,偺帪掕悢偱揹棳偼棳傟偰偄傑偡乯

Attack CV偺埵抲傑偱弶傔偵output偑媫懍掅壓偡傞偺偑 CV揹埑偺栶栚偱偦傟埲崀偺 CR僇乕僽偼 Attack CV偵偐偐傢傜偢摨偠偩偑栚昗廩揹揹埑偑嵎偑偁傞偺偱僇乕僽偑備偭偔傝尒偊偨傝憗偔尒偊偨傝偡傞偲偄偆僩儕僢僋丅

release帪傕摨條偵relase CV偺揹埑傑偱Out Put揹埑偼媫忋徃偟偦傟埲崀偼 CR偺帪掕悢偱曻揹偟傑偡丅丂偙偺応崌偼attack偲媡偵rekase CV偑戝偒偄曽偑relase time偑抁偔側傝傑偡丅

*1:

Attack CV=0V帪偱傕D1偺揹埑崀壓暘偲R偺揹埑崀壓暘偑傞偺偱栺2V偔傜偄傑偱偟偐D1 ON嬫娫偱壓偑傜偢偦傟埲崀偼22Mt偲0.1uF偺帪掕悢偱壓崀丅 attack CV偑3V埲忋偵側傞偲D1丄R偵棳傟傞揹棳偑媫掅壓偡傞偺偱傎傏attack CV嬤偔傑偱Out丂Put偼偼偠傔偺僞僀儈儞僌偱壓偑傞丅

I00偲I01

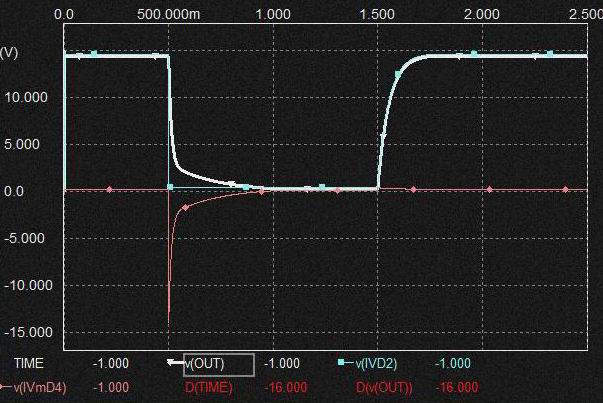

1: ATTACK Phase

敀: OUT PUT

烌: D3 A-K娫揹埑

悈: D4 A揹埑

Attack phase帪 Relase CV偑 out put偵塭嬁傪梌偊側偄傛偆偵偡傞偨傔偵偼 D3偑OFF偡傞昁梫偑偁傞丅偙偺偨傔偵偼D4偑 ON偟偰D4偺傾僲乕僪偑GND儗儀儖傛傝彮偟戝偒偄抣(0.4V掱搙)偱偁傟偽D3 OFF丅丂偙偺帪D4偺宱楬偵棳傟傞揹棳偑I01偵側傞丅

attack偑掕忢忬懺偱偍偪偮偄偰Out Put偑0V嬤偔偵側偭偰傕D3傪ON偡傞偺偵懌傝偆傞揹埑偵偝偣側偄嶌梡丅偡側傢偪 relase CV偺抣偑戝偒偔偲傕D3傪ON偝偣偰丂Cap.偺揹埑傪忋徃偝偣側偄傛偆偵偡傞丅

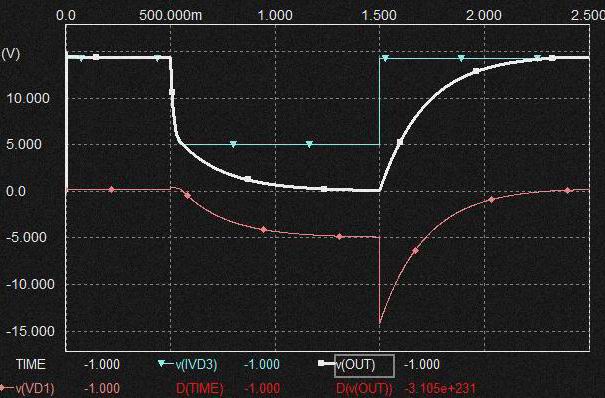

2: RELASE Phase

D1帺懱偼Attack phase偺巒傔偺堦弖偩偗ON偟偰偦傟埲崀偼OFF側偺偱 D1偑偁傟偽 relase phase帪Attack CV 偺抣偑彫偝偔 偲傕out put偺揹埑傪掅壓偝偣傞偙偲偼側偝偦偆偱偁傞偑 D2偑柍偄偲Key OFF帪偺 oit put 揹埑+15V傪曐帩偱偒側偄偺偱 D2偼昁梫側傛偆偩丅

敀: OUT PUT

烌: D1 A-K娫揹埑

悈: D2 K揹埑

D1偺Vak偼忋恾偱偼500mS晅嬤偱堦弖0.6V掱搙偵側傝懄壓崀偟偰D1 OFF丅

D2偑柍偄偲Key OFF嬫娫偱D1偺僇僜乕僪揹埵偑掅壓偟偰偟傑偆丅

Attack / Relase 僇乕僽偺摿挜

Attack CV偺抣傪壜曄偟偨偲偒偺Attack僇乕僽偺曄壔傪帵偟傑偡丅

偙偺恾偺傛偆偵 attack偺僇乕僽偼2抜峔惉偵側偭偰偍傝嵟弶偼 Attack CV 偺抣傑偱媫寖偵Out put儗儀儖偑棊偪傑偡丅 偙偺応崌偺廩揹揹棳偺宱楬偼2偭偁傝堦偮偼 22M偲0.1uF偺帪掕悢丅丂偦傟偵壛偊偰 +15V偲attack CV偺抣偺嵎暘娫偵懳偟偰 0.1uF偺 cap.偲D1偺diode偺旝暘掞峈偺帪掕悢偱Out Put儗儀儖偑掅壓丄D1偑OFF偟偰偐傜偼22M偲0.1uF偺帪掕悢偱悇堏偟傑偡偺偱偦傟埲崀偼attack CV偺抣偵傛傜偢摨偠僇乕僽側偺偱偡偑巆傝偺摓払嫍棧偺堘偄偵傛偭偰堘偆僇乕僽偺傛偆偵尒偊偰偟傑偆丅丂偡側傢偪傑傞偱儕僯傾億儖僞儊儞僩偺傛偆側怳傞晳偄丅

AttackCV=15V帪偼傎傏 22M偲0.1uF偺帪掕悢偺僇乕僽偱媡偵Attack CV=0V帪偼Key ON偱懄0V嬤偔(幚嵺偼2V偔傜偄)傑偱output儗儀儖偑壓偑偭偰偐傜22M偲0.1uF偺帪掕悢僇乕僽偑巒傑傝栚昗抣偑偡偖偦偙偵偁傞偺偱僇乕僽傕偡偖廔椆丅丂attack CV=7V帪偼2僷僞乕儞偺僇乕僽偑暘偐傟偰偼偭偒傝尒偊傑偡丅

attack帪偺 D1偺 ON/OFF摦嶌偲0.1uF偺 capacitor傊偺廩揹娭學偲Relase帪偺D3偺ON/OFF摦嶌偲0.1uF偺Capacitor傊偺曻揹娭學偼 EG偲偄偆傛傝偼VCO偺摦嶌偲崜帡偟偰偄傑偡丅丂傑偨Attack帪丄release CV偑output偵塭嬁偟側偄傛偆偵D3偑Off偡傞偨傔偵偼娫愙揑偵D4偑昁梫偱丄Relase帪attack CV偑output偵塭嬁偟側偄傛偆偵D1偑OFF偡傞偨傔偵傕D2偑昁梫偲偄偆娭學偵側偭偰偍傝偙傟偑堦弖diode ring偲摨偠攝抲偵側偭偰偄傞偺偑柺敀偄丅 僄儞償僃儘乕僾僇乕僽偺僊儈僢僋偼儕僯傾億儖僞儊儞僩偺僇乕僽偺惈幙偵傕嫟捠揰偑偁傞偲偙傠偑柺敀偄丅

偪側傒偵忋婰偺恾偱 AR偺Envelope偺宍偑捠忢偲斀揮偟偰偄傑偡偑Lambda偵巊梡偟偰偄傞Tone generator IC S10430偺Vss=+15V丄Vdd=GND偲偄偆揹埑偺梌偊偐偨偍傛傃 Key ON偱 GND丄 KEY OFF偱 +15V偺娭學偵懳偟偰偺envelope側偺偱媡揮偟偰偄傞傛偆偱偡丅

傑偨偙傟傜偺暘廃壒尮偲偄偆偺偼嬮宍攇偺敪怳婍弌椡傪 Gate夞楬偱EG偱 gateing偟偰嵟廔弌椡偡傞偨傔捠忢偺VCA偺傛偆側2徾尷偺弌椡偵偼側傜側偄偺偱弌椡偼1徾尷偲偄偆偐曪棈慄偼曅懁偺傒偵晅偒傑偡丅

偙偺傛偆側曅懁偺傒曪棈慄偑偁傞峔憿偺暔偑慡尞斦敪怳壒尮偵偼懡偄偱偡丅丂偙傟偼摉慠偲偄偆偐奺尞斦偵synth偱巊偆VCA偼COST揑偵巊梡偱偒側偄偐傜偱偟傚偆丅

<2019/11/09 rev0.1>