�O�i�����{��̐���

�@��i�Ŏl���{�̊���A���������������Ă����Ƃ킩��ƁA������i���āA�O�i�����{�ł͂ǂ����낤���A�Ƃ����Ȃ��l�����B���{��10dB���x�̃Q�C�����Ƃ��ƁA1.4G���0dBm���x�̏o�͂ő����B�����Ȃ�A���U�i�̕��S�͏��Ȃ��A���M�����Ȃ��̂ň���x���悭�Ȃ�A�X�v���A�X���������₷���̂ł͂͂Ȃ����A�ƍl�����B�܂��A�ړ��p�ɂ͑�ȏ���d���̓_�ł��L���ƂȂ�B�����A��������ς��������A�m�E�n�E�����߂A�Ȃ�Ƃ����邾�낤�B

1..�O�i�����{���

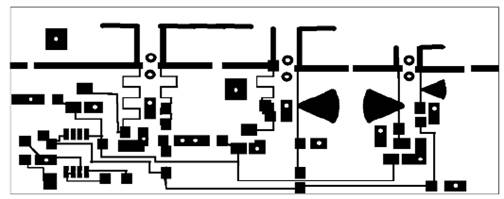

![]() �@�܂��́A�O�i�����{��11450Mhz���o�͂���������Ă݂��BFET�ɂ͎O�i�Ƃ��ɓ���̗e�Ղ�NE3210S01���g���A�h���C����R100�������5V�����������B(�h���C���d��3-4V���x)����ŁA1.4G��̓��͂�8�{����11450Mhz���o�͂���B

�@�܂��́A�O�i�����{��11450Mhz���o�͂���������Ă݂��BFET�ɂ͎O�i�Ƃ��ɓ���̗e�Ղ�NE3210S01���g���A�h���C����R100�������5V�����������B(�h���C���d��3-4V���x)����ŁA1.4G��̓��͂�8�{����11450Mhz���o�͂���B

�@�ŏ��͏o�͂�1.4G�����āA��i�ڂ��珇�Ƀh���C���̃g���b�v��1.4/2.8/5.6G�ƒ�������B

�A���̌�A�i�Ԃ̌���������B

�B�Ō�ɑS�̂��o�͂����Ȃ��璲������c�Ƃ����菇�Œ��������B���ʁA0.5mW���͂�8mW�o�͂�����ꂽ�B�ǔ��̑O�i��1mW�o�͂ő����B1.4G�̓��͕��͕s�v�c�ƃX�^�u���S���v��Ȃ������B�������A���̋ǔ��ɏo�͂̑傫��(13dBm���x)�O�i��������A�X�b�|�k�P�Ȃǂŗ]�v�ȃX�v���A�X���o�Ă��܂����B47G�p�ɑg�ݍ��ނ��߁A���U���Ƃ̊ԂɎO�i�L���r�e�B��BPF�����A���X�𑽂����ă��x�����킹���p�Ƃ����B

2.�O�i�����{��@����2

�ꖇ�ڂ����������������̂ŁA24G�̈ړ��p��11370M���o�͂��锪���{�삵�Ă݂��B�O�l�AFET�ɂ�NE3210S01���O�i�g�����B�����R���f���T�ɂ́A1.4G 33pF /2.8G 15pF/ 5.6G 6pF/11G 1pF��p�����B 1.4G�̃g���b�v�͑O��ƌ`���ς������A�傫���ꏊ���Ƃ�̂���_�ł���B����́A1.4G���͕���6pF�̃g���}�����Ē�������ƈ�i�ڂ̓��삪�傫���ω������B��p�^�[���ɂ́A�g���}��p�X�R���݂���O���E���h�������ɓ���Ă������B���ʁA1.4G��0.5mW��11370M��8mW�A�O�a�o�͂�����2mW���x��12mW���x�ƂȂ����B�Ȃ��A���{�i�̓����Ƃ���(?)�A���͂����炵�Ă�����0.3mW���x�ŃK�N�b�Əo�͂��������B�����삾���瓖����O����??�����A�g���b�v�̃c�����܂��Â��̂��A2G���̃X�v���A�X��-20dB���x�ɂƂǂ܂��Ă���B

1.4G�̃g���b�v�͑O��ƌ`���ς������A�傫���ꏊ���Ƃ�̂���_�ł���B����́A1.4G���͕���6pF�̃g���}�����Ē�������ƈ�i�ڂ̓��삪�傫���ω������B��p�^�[���ɂ́A�g���}��p�X�R���݂���O���E���h�������ɓ���Ă������B���ʁA1.4G��0.5mW��11370M��8mW�A�O�a�o�͂�����2mW���x��12mW���x�ƂȂ����B�Ȃ��A���{�i�̓����Ƃ���(?)�A���͂����炵�Ă�����0.3mW���x�ŃK�N�b�Əo�͂��������B�����삾���瓖����O����??�����A�g���b�v�̃c�����܂��Â��̂��A2G���̃X�v���A�X��-20dB���x�ɂƂǂ܂��Ă���B