僱僢僩偵弌夞偭偰偄傞CEM IC偺僨乕僞乕僔乕僩偼堦晹偺chip(CEM3394/CEM3350摍)傪彍偄偰偲偰傕儁乕僕悢偑彮側偄偱偡丅丂CEM3340偺僔乕僩偼6儁乕僕偲撪梕傕徻偟偄曽偱偟傚偆丅

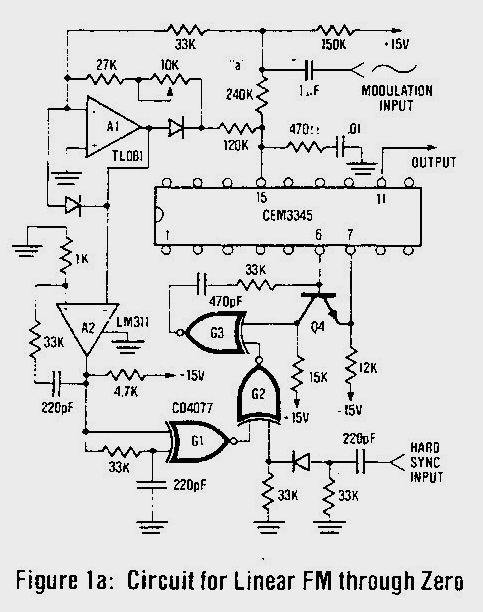

傑偢偼昡壙儃乕僪揑側夞楬傪慻傫偱尒傑偡丅丂夞楬偼 CES 偺 CEV3301昡壙儃乕僪偺VCO夞楬偲摨條側夞楬偲偟傑偟偨偑庤帩偪晹昳偺搒崌忋抣偺堘偆傕偺傪偄偔偮偐巊梡丅

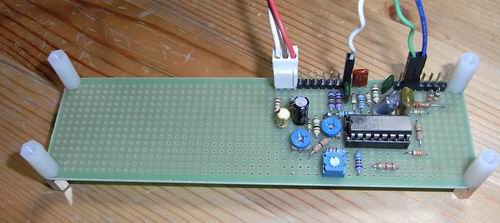

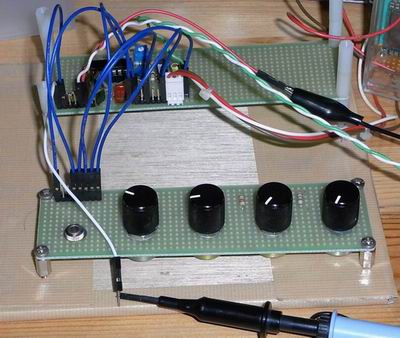

幨恀偺傛偆偵 廐寧偺嵶挿偄婎斅偵慻傫偱傒傑偟偨丅丂偙偺掱搙偺晹昳婯柾偱嶰妏攇丄嫎攇丄嬮宍攇弌椡,Sync, LineaFM OK丄 scale, span偺壏搙曗彏撪憼,10octave偔傜偄偼埨掕偟偰敪怳偱偒傞僼儖巇條偺VCO偺偺僐傾晹暘偑姰惉偟偰偟傑偄傑偡丅丂偙偺夞楬偱偁傟偽偙偺婎斅偵2VCO暘偑搵嵹偱偒傑偡丅

扥擮偵攝慄僠僃僢僋偼偟偨偺偱堦敪偱摦偒偼偟傑偟偨偑偳偆傕摦嶌偑曄偱偡丅 CV傪0V偐傜15V傑偱壜曄偟偰偄傞妱偵偼廃攇悢曄壔偑撦偄偱偡丅丂攝慄偵娫堘偊偼側偄傛偆側偺偱堦晹偺掞峈偺掞峈抣傪庤帩偪偺掞峈偱抲偒姺偊偨偙偲偑尨場偐偲巚偄傑偟偨偑偦偆偄偆偙偲偱偼側偄傛偆偱偡丅丂30擭埲忋傕慜偺僷乕僣偱偼惓忢偵摦偐側偄偺偐偲傕巚偄偮偮夞楬恾傪嵞搙挱傔偰傒傞偲Linea 擖椡(Iref掞峈晅嬤乯偐傜 GND偵偮側偖掞峈470兌傪1M偲娫堘偊偰攝慄偟偨偙偲偵婥偯偒掞峈傪岎姺偟偨傜惓忢偵摦偔傛偆偵側傝傑偟偨丅丂VCO偺幚尡傪偡傞偺偵枩擻婎斅傪巊偭偨傜榁娽偑偗偭偙偆棃偰偰偮傜偐偭偨偱偡丅婎斅棤偑嬧儊僢僉傪偟偰偁傞暔偼旀傟傑偟偨丅丂摵敁偺曽偑旀傟傑偣傫偺偱崱屻偼廐寧偺巻僼僃僲乕儖婎斅傪巊偆傛偆偵偟傑偡丅

昡壙夞楬偼忋恾偺傛偆側傕偺偵側傝傑偡丅丂側偵傛傝偙偺IC 1偮偩偗偱懠偵OPAMP摍傕偲傝偁偊偢偼昁梫側偄偲偄偆偺偼偐側傝偺儊儕僢僩偩偲巚偄傑偡丅丂徚旓揹棳傕僾儔僗懁偑4mA, 儅僀僫僗懁偑5mA掱搙側偱庤寉偱偡丅丂戝傑偐偵僗働乕儖挷惍傪偟偰CV傪0V偐傜15V擖椡偟偰傒偨偲偙傠丂CV-0V偱栺1Hz丄 CV=14.3V偱栺14KHz偺敪怳傪妋擣偟傑偟偨丅丂悇彠夞楬偱偼 Iref梡偺掞峈偑Vcc=15V偱1.5M兌偩偭偨偺偱Iref=10uA偩偭偨偺偱偡偑1.5M偺嬥旂偑柍偐偭偨偺偱1M傪巊梡偟偨偺偱Iref=15uA偲側傝傑偡丅丂Iref偼3uA偐傜15uA偺斖埻偱愝掕偝傟偰偄傟偽傛偄傛偆側偺偱偦偺斖埻偵偼擖偭偰偄傑偡偑幚梡帪偵偼悇彠垻抣偺1.5M兌偵偟偨曽偑傛偝偦偆偱偡丅

module偲偟偰幚嵺偵巊梡偡傞応崌偼 scale愝掕偺敿屌掕傪懡夞揮偵偟偨曽偑傛偄偐偲偐丄 屌掕 CV傪梌偊傞帪偺曽朄偲偟偰Octave愗傝懼偊傪偮偗傞偺偐楢懕壜曄偱 Coase tune偲偡傞偐擸傓偲偙傠偱偡丅丂傑偨奜晹CV=0V帪偺OFFset揹埑偡側傢偪initial偺敪怳廃攇悢偺愝掕傪寛傔傞昁梫偑弌偰偒傑偡丅丂A4=440Hz偲偟偰C1偺僉乕偱65Hz偲偡傞偲偙偺帪 Key CV=0V偲偡傟偽 偙偺幚尡夞楬偱偼initial偺OFFset揹埑偼6V掱搙(6octave偺offset)偁傟偽傛偄偺偱偟傚偆丅

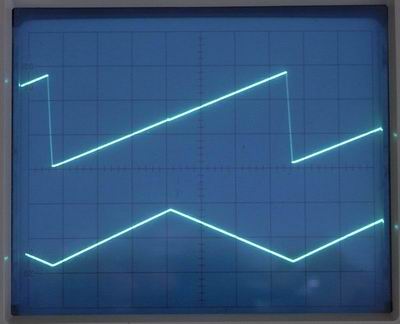

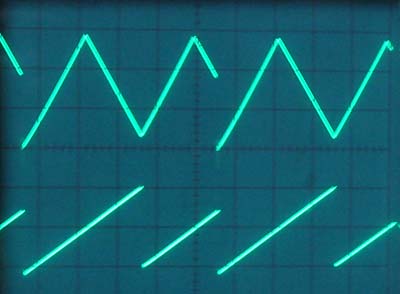

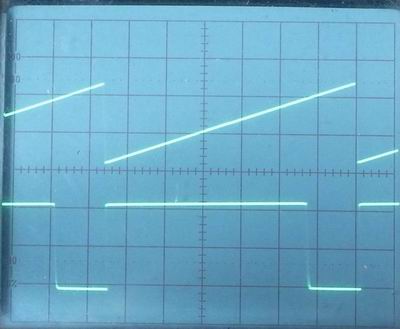

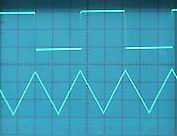

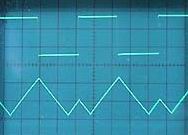

忋偺幨恀偵弌椡攇宍傪帵偟傑偡丅 CEM3340偼嶰妏攇傪尮攇宍偲偟偰敪怳偟丄偦傟傪尦偵嫎攇傪摼傞僞僀僾偺VCO偱偡偑幨恀傪傛偔尒傞偲嶰妏攇傪愜傝嬋偘偰嫎攇傪摼傞嵺偺宲偓栚偑妋擣偱偒傑偡丅丂幨恀偺攇宍偼14KHz偔傜偄偺敪怳攇宍側偺偱偡偑嫎攇偺棫壓傝偑寢峔備傞傗偐偱偡丅丂敪怳廃攇悢偑彫偝偄帪偺攇宍偼棫壓傝偑偦傟傎偳婥偵側傝偼偟傑偣傫偺偱幚梡柺偱偼偁傑傝栤戣偼側偄偱偟傚偆丅

敿屌掕POT偩偗偺憖嶌偱偼側傫側偺偱CV敪惗婍偲偟偰Coase, Fine, PW偺 volume傪偮偗偰幚尡偟偰傒傑偟偨丅丂VOLUME傪偮偗偨偺偱傗偭偲嬮宍攇弌椡偲PW偑壜曄偱偒傞傛偆偵側傝傑偟偨丅

丂

丂

崲偭偨偙偲偵PW偺抣傪摦偐偡偲僺僢僠偑傢偢偐偱偡偑曄摦偟偰偟傑偄傑偡丅丂尨場傪扵偭偰尒傞偲PAIA偺KIT偺傑偹傪偟偰奜晹揹尮擖椡抂巕偵 C偲R偱CRfilter(C=10u, R=100兌)傪峔惉偟偰偍偄偨偺偱偡偑PW傪壜曄偡傞偲CEM3340偵撪憼偺僐儞僷儗乕僞偺徚旓揹棳偑曄壔偡傞傜偟偔R偵傛傞揹埑崀壓偑曄壔偟偰偟傑偆偨傔偱丄 偦偙偐傜Vref揹埑傪庢偭偰偄偨偨傔Iref偑傢偢偐偵曄摦偟偰偟傑偆偱偡丅R傪庢傝奜偟偨傜偙偺尰徾偼側偔側傝傑偟偨丅丂偆偭偐傝偟偰偄傑偟偨偑幚尡偟偰婥偯偄偨偙偲偲偟偰偙偺傛偆側CRfilter傪偮偗傞偺側傜Vref偼撈棫偟偰梡堄偟側偗傟偽側傜側偄偲尵偆偙偲偱偡丅丂

偝傜偵婎斅傪墴偡偲敪怳廃攇悢偑曄壔偟偰偟傑偄丄墴偡偺傪傗傔傞偲尦偵栠傞偲偄偆尰徾偑敪惗丅丂偳偆傕Offset揹埑傪梌偊偰偄傞晹暘偺敿揷晅偗偑偁傗偟偄丅丂偦偺晹暘偺敿揷傪惙傝側偍偟偨傜夝寛偟傑偟偨丅

CEM3340偺奺婡擻

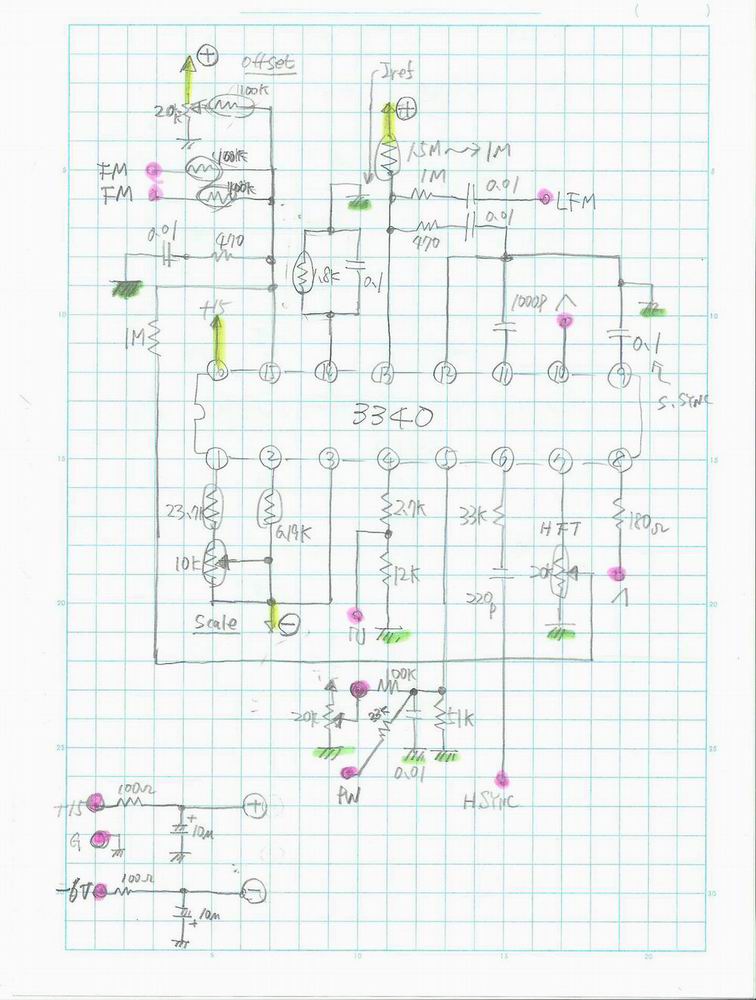

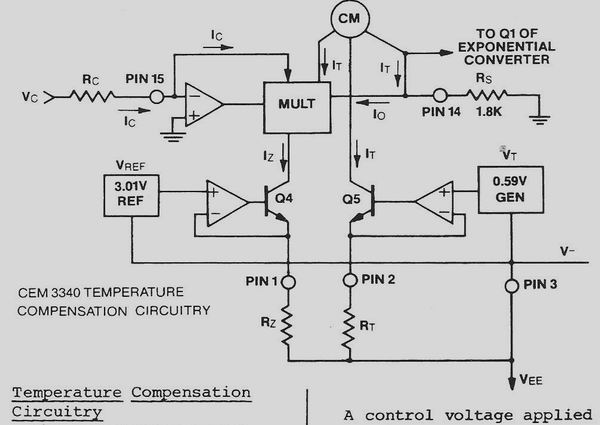

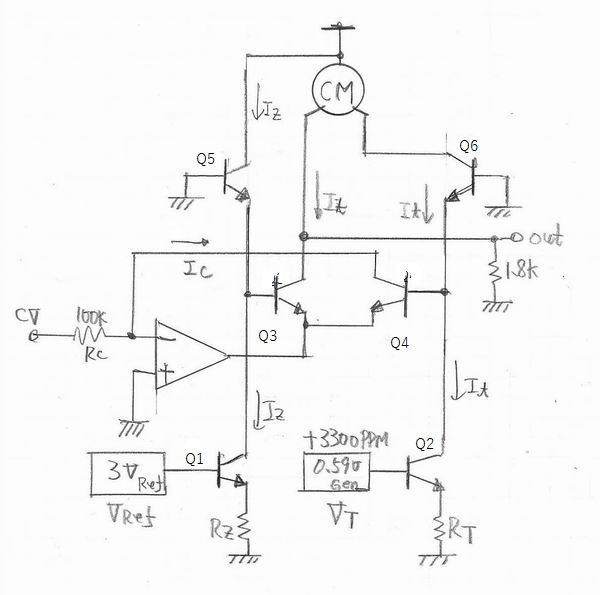

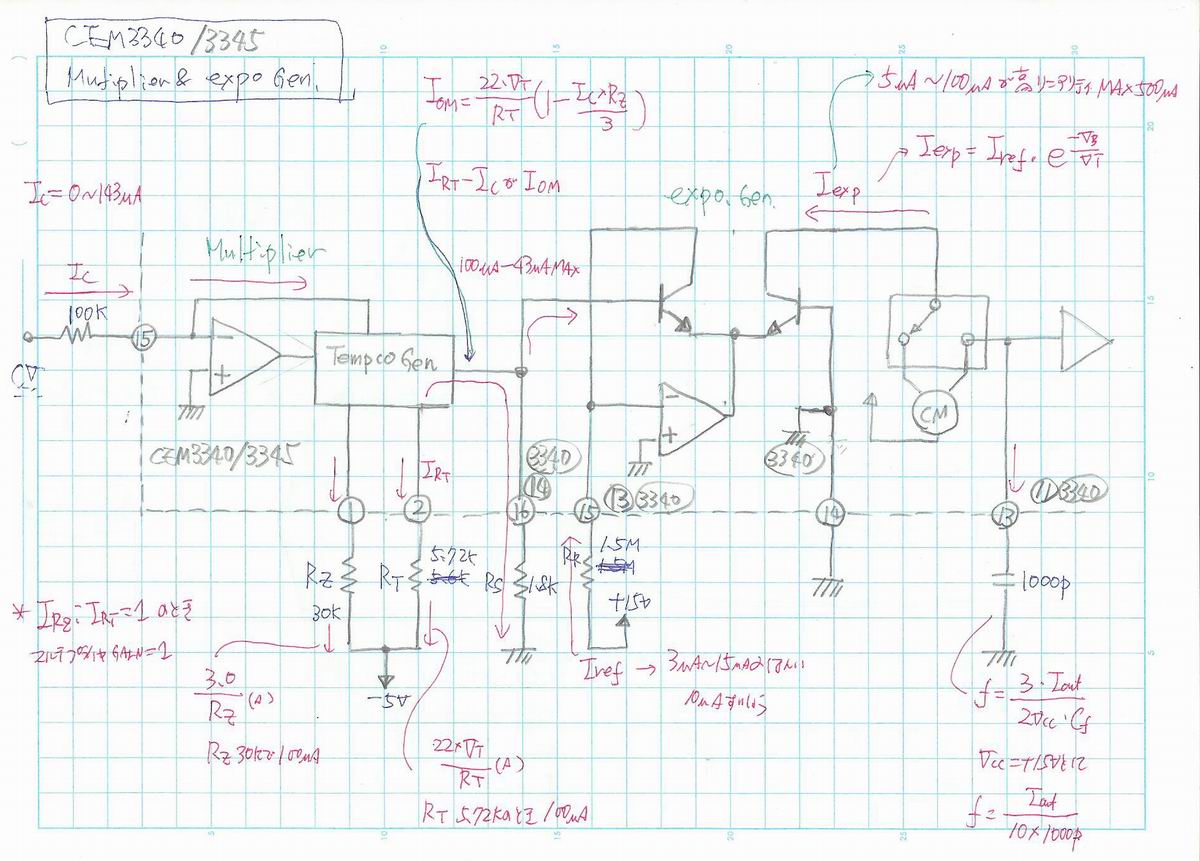

CEM3340偼 antilog amp偺慜抜偵偁偨傞summing amp偺GAIN乮multiplier偺攞棪乯傪壏搙偵懳偟偰壜曄偡傞(*1)偙偲偱 antilog amp偺scale 曗彏傪峴偆曽幃偱偡偺偱偙偺愝掕偑側傟側偄偲傢偐傝偵偔偄偱偡丅埲壓偵 summing amp廃傝偲 antilog amp傑傢傝偺峔惉恾傪帵偟傑偡丅

* 忋恾偺 PIN No偼 CEM3345偺Pin No偵懳墳丅

Pin 1偲 Pin2偵偮偗傞掞峈偵傛偭偰 Summing AMP偵撪憼偝傟偰偄傞 multiplier偺GAIN傪挷惍偡傞傛偆偱偡丅丂掞峈Rt偵棳傟傞揹棳偼丄丂Irt= 22* Vt/Rt偱媮傑傝傑偡丅

Irt傪100uA偲偡傞偲Rt偼 5.72K兌偵側傝傑偡丅丂師偵Rz偱偡偑Rz偵棳偡揹棳傪Irt偲摨偠100uA偵偡傞偵偼丄丂IRz-3.0/Rz側偺偱丂Rz=30K兌偲側傝傑偡丅

Multiplier偺GAIN傪1偵偡傞偨傔偵偼 Irt=Irz偵偡傟偽偄偄傛偄偆偱偡丅 丂Irz,Irt偺愝掕偵 -揹尮偺揹埑偼塭嬁偟側偄傛偆偱偡丅

偙偺summing AMP偺弌椡揹棳偑antilog AMP偺擖椡Q1偺儀乕僗偵擖椡偝傟傞傢偗偱偡偑丄 儀乕僗- GND娫偵偮側偑偭偰偄傞掞峈Rs傪1.8K偲偡傞偲summing AMP偺summing node偵愙懕偝傟傞掞峈傪100K兌偵偡傞偙偲偱 1oct/V偺娭學偑摼傜傟傑偡丅

奜晹CV=0V帪偙偺100uA偺Irt偑Rs偵棳傟傞偙偲偵側傝丄CV傪忋偘偭偰偄偭偰Icv偑棳傟傞偲Irt-Icv偺抣偑Rs偵棳傟傞傛偆偵側傞偺偱Icv=100uA偺帪 Multiplier弌椡Iom偼0偲側傝傑偡丅丂Iom=(22*Vt/Rt)(1-(Ic*Rz/3))

堦曽antilog AMP懁偼 Rr偱Iref偑寛傑傝傑偡丅丂15斣抂巕Vcc娫偵1.5M兌偺Rr傪偮側偖偲Iref = 10uA偲側傝 Q1偺Vb抂巕(antilog amp擖椡)偑0V偺帪 antilog AMP弌椡偼10uA偵側傝傑偡丅丂Iexp=Iref*e^(1Vb/Vt)

|

antilog 偺擖椡偺儀乕僗揹埵Vb偼 Icv=0V偱嵟戝抣偱Ic偑憹偊傞偵廬偭偰揹埵偑掅壓,Ic=Irt偱0V偦傟埲崀偼儅僀僫僗偲側傝傑偡丅丂偙偺偨傔 塃懁偺antilog 梡偺僩儔儞僕僗僞偺 Vbe偼Ic偺忋徃偲嫟偵憹戝偟傑偡丅

CV偑彫偝偄偲Ic偑戝偒偄偺偱乮It-Ic乯偼彫偝偔掞峈Rs偺揹埵偑戝偒偄偲antilog偺嵍懁偺 Tr.偺Ve偑崅偄偺偱塃懁偺Tr.偺Vbe偼彫偝偄偺偱antilog揹棳偼彫偝偄丅 CV偑戝偒偄偲Ic偑彫偝偄偺偱乮It乕Ic乯偼戝偒偔掞峈Rs偺揹埵偑彫偝偄偲antilog偺嵍懁偺 Tr.偺Ve偑掅偄偺偱塃懁偺Tr.偺Vbe偼戝偒偄偺偱antilog揹棳偼戝偒偄丅 |

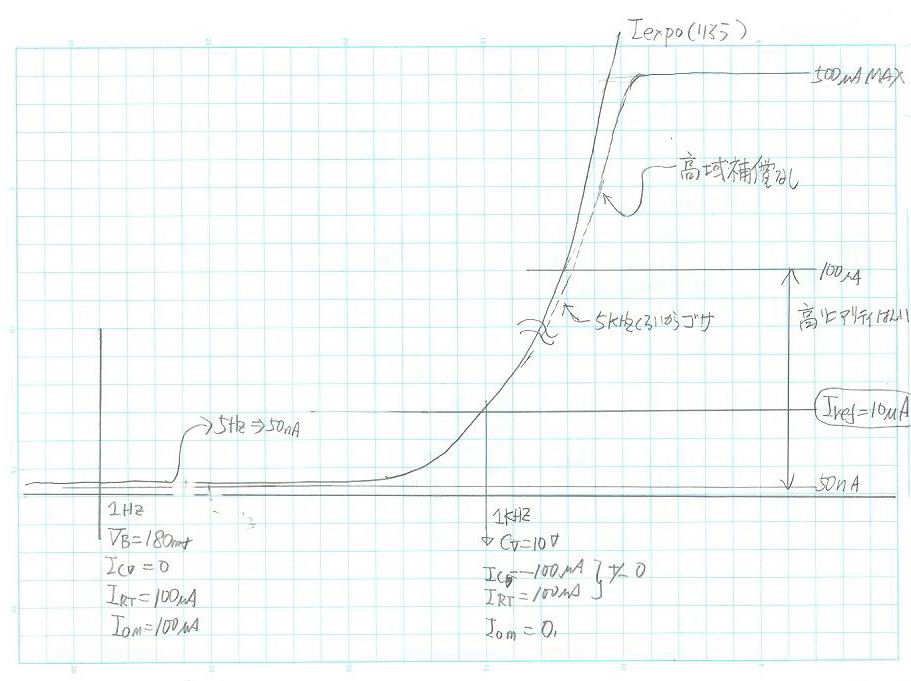

Icv偺抣偼捠忢0偐傜143uA傑偱偩偦偆偱偡丅丂Iexp偺斖埻偑50nA偐傜100uA偺斖埻偑崅儕僯傾儕僥傿嬫娫側傛偆偱丄 偨偲偊偽Iref=10uA偲偡傞偲CV=0V偱 Iexp偼10nA掱搙傑偱掅壓偟傑偡偺偱CV, Icv傪儅僀僫僗偵偡傞偙偲偼偁傑傝堄枴偑柍偄偲偄偆偙偲偱偟傚偆偐丅

Icv偺擖椡斖埻偼 0偐傜 143uA偲尵偆偙偲偱丄傛偭偰Iom=100uA偐傜-43uA側傝傑偡偺偱 揹埑Vb偼 CV=0V帪 180mV丄 CV=10V帪 0V ,CV=14.3V帪 -77.4mV偲側傝傑偡丅

13斣抂巕偵偮側偑傞Timmnig capactor丂Cf偲敪怳廃攇悢偺娭學偼丂F=(3*Iexp)/(2Vcc*Cf)

Cf=1000P丄 Vcc=+15V偲偡傞偲 F=Iexp/10*1000P丂偲側傝 Iexp=100uA偱10K Hz丂Iexp=50nA偱 5Hkz偲側傝傑偡丅丂偡側傢偪CV=10V偱1KHz丂CV=0V偱1Hz偲側傝傑偡丅

| 丂CV=00V | 丂F= 0.975Hz | 丂Iexp=9.75nA |

| 丂CV=01V | 丂F= 1.95Hz | 丂Iexp=19.5nA |

| 丂CV=02V | 丂F= 3.9Hz | 丂Iexp=39nA |

| 丂CV=03V | 丂F= 7.8Hz | 丂Iexp=78nA |

| 丂CV=04V | 丂F=15.6Hz | 丂Iexp=156nA |

| 丂CV=05V | 丂F=31.2Hz | 丂Iexp=312nA |

| 丂CV=06V | 丂F=62.5Hz | 丂Iexp=625nA |

| 丂CV=07V | 丂F=125Hz | 丂Iexp=1.25uA |

| 丂CV=08V | 丂F=250Hz | 丂Iexp=2.5uA |

| 丂CV=09V | 丂F=500Hz | 丂Iexp=5uA |

| 丂CV=10V | 丂F=1KHz | 丂Iexp=10uA |

| 丂CV=11V | 丂F=2KHz | 丂Iexp=20uA |

| 丂CV=12V | 丂F=4KHz | 丂Iexp=40uA |

| 丂CV=13V | 丂F=8KHz | 丂Iexp=80uA |

| 丂CV=14V | 丂F=16KHz | 丂Iexp=160uA |

Coase/Fine/KBD CV偺斖埻傪峫偊昁梫偵墳偠偰Initial CV揹埑傪梌偊傟偽偄偄偱偟傚偆丅 Iexp偼 MAX 500uA傑偱偼弌椡偱偒傞偦偆偱偡丅丂傑偨 Iref偼 3uA偐傜15uA偺斖埻偱巊梡偡傞傛偆偵彂偐傟偰偍傝10uA偵愝掕偡傞偺偑悇彠偝傟偰偄傑偡偺偱 Vcc=15V帪 Rr=1.5M兌偲側傞傛偆偱偡丅

|

1: CEM3340/3345偺AntiLog AMP偺Scale壏搙曗彏曽朄 * antilog amp偺Scale曗彏偲Offset曗彏偺昁梫惈 offser曗彏偼晛捠偺曽幃丄OP AMP偺FB loop偺拞偵Tr.偺C-E娫傪擖傟偰掕揹棳僪儔僀僽偡傞僞僀僾乮忋婰偺峔惉恾)丅Scale曗彏偼壓婰偺曽朄丅 +3300ppm偺tempco摿惈偺multplier傪峔惉偡傞偙偲偱antilog AMP偺壏搙偵懳偡傞僗働乕儖曄摦 -3300ppm傪僉儍儞僙儖偡傞曽幃偺傛偆偱偡丅丂

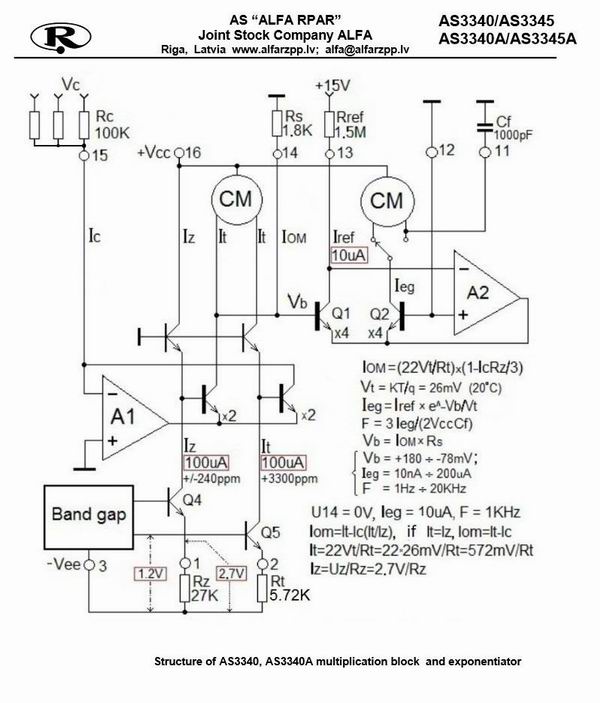

忋恾偼 CES偺news letter偵宖嵹偝傟偰偄偨夞楬偱偡丅丂屄乆偺憰抲偺徻嵶偼柧婰偝傟偰偼偄傑偣傫偑 Vt(擬揹埑)偺曄壔傪専弌丄偄傢備傞PTAT揹埑敪惗尮傪棙梡偟偰偦傟偲CV揹埑偺忔嶼傪峴偆偙偲偱師抜偺Antilog偵懳偟偰惓偺壏搙摿惈偵偟偰antilog偺T偺梫慺傪僉儍儞僙儖偟傑偡丅壓偺ALFA偺datasheet傪尒傞偲BAND Gap儕僼傽儗儞僗夞楬偺惓偺壏搙摿惈傪帩偮弌椡傪棙梡偟偰擖椡(CV)偵懳偟偰忔嶼傪偟偰偄傞偺偱偟傚偆丅揹棳忔嶼婍偺夞楬摦嶌偑傛偔傢偐傝傑偣傫偑(*0)丅

嵍偺揹棳尮 Iz: reference current generator Iom=It -Ic * (It/Iz) 偙偙偱It偼+3300ppm偺壏搙摿惈傪帩偮揹棳偲側傞傛偆偱偡丅丂椉揹棳抣偼偦傟偧傟丄

It= 0.59V / Rt 偱媮傑傝椉幰傪摨偠抣偵偡傞偙偲偵傛偭偰擖椡 Ic偺1攞偺+3300ppm壏搙摿惈傪帩偭偨Io偑弌椡偝傟傞傛偆偱偡丅丂幚嵺忋偺奺掕悢偼埲壓偺幃偱摼傜傟傑偡丅

Multiplier Output揹棳: Iom 忋恾忋偺Vt=590mV Gen偺堄枴偼 Kt/q=26.8mV *22 =590mV偐傜偔傞傕偺偩偦偆偱偡

ALFA偺恾傪彂偒捈偟偰傒傑偟偨丅傛偔尒傞偲1徾尷偺multiplier偵崜帡偟偨夞楬偱偁傞偙偲偑傢偐傝傑偡丅(偲偄偆偐偙偺夞楬偱1徾尷偺multiplier傪峔惉偟偰偄傑偡丅乯 CV in偺晹暘偼antilog amp偱偄偆偲偙傠偺 Linear IN晹暘側偺偱OPAMP偲Q4偱Log Amp偑宍惉偝傟傞宍偵側傝Q3傎偦傟偵懳偟偰EXPO側偺偱antilog偱偡丅寢壥Q3偺Ic偼CV in偵懳偟偰Linear弌椡偱偡丅 忋恾偺僇儗儞僩儈儔乕偼It - Ic = Iom傪幚尰偡傞偨傔偺偟偔傒偱CV=0V帪 It=Iom偱丄CV偑憹壛偡傞偲Ic偑憹偊偨暘偼Q3偺僐儗僋僞揹棳偲側傝僇儗儞僩儈儔乕偐傜偺巆傝偑Iom偵暘棳偡傞丅 偪側傒偵RC4200僞僀僾偺multiplier偼壏搙偺塭嬁傪庴偗側偄偐傜偙偦(*0)丂Vt偵斾椺偟偨揹棳尮傪梡偄偰惓偺學悢傪帩偮CV抣傪摼丄師抜偺antilog amp偑晧偺壏搙摿惈傪帩偮偨傔偍屳偄偱僉儍儞僙儖偡傞偲尵偆偙偲偱側偐側偐傗傗偭偙偟偄偱偡丅忋恾偵偍偄偰儕僼傽儗儞僗偲側傞壏搙偵塭嬁傪庴偗側偄Band Gap揹埑尮偼Iz偑+/- 240ppm偲尵偆堄枴偼BANDGAP揹埑尮偺壏搙學悢偺傛偆偱偡(堦斒偵悢廫偐傜悢昐ppm偩偦偆偱偡)丂塃懁偺揹埑尮偼壏搙偵斾椺偟偰+3300ppm偺壏搙摿惈傪帩偮揹埑尮丅 *0: 50ppm掱搙偺壏搙學悢偼偁傞傛偆偱偡偑丅 Multiplier偺応崌偼LogAMP偺惓偺壏搙摿惈偲antilogAMP偺晧偺壏搙摿惈偱壏搙曄壔傪僉儍儞僙儖偟傑偡偑CEM3340偺応崌偼惓偺壏搙摿惈傪帩偭偨揹埑尮傪儕僼傽儗儞僗偲偟偨MIXER偲偄偭偨姶偠偱偟傚偆偐丅

RC4200type偺multiplier偺摦嶌偲摨條偵峫偊傞偲丄 0: Vt偲Q5偺Vbe偑 Xin偵懳墳(Log) 丂CV in偑 Yin偵懳墳 (Log * AntiLog) 丂Vref(Vz)偲Q5偺Vbe偑Scale偵懳墳(Log)側偺偱 Vt * Vcv / Vref偲偄偆忔梋嶼 1: OP AMP偺FB loop撪偵C-E娫偑偁傞曽偺Tr. Q4偺Vbe偼CV偵懳偟偰LOG AMP丅 2: 傑偨Vt偑傜傒偺Q6偺Vbe偺曄壔傕Ic偑僄儈僢僞僼僅儘儚偩偐傜Ic偺儕僯傾側曄壔偵懳偟偰LOG 摦嶌偱偙傟偑Q4偺儀乕僗偵偮側偑偭偰偄傞偑Q4偺Vbe4偼偙傟偱偼曄壔偱偒側偄偺偱偱Q6Ve偺曄壔暘偩偗Q4偺Ve偑暲峴堏摦偟Q4偺僄儈僢僞揹埵偼LOG偺壛嶼丅 3: Q3偼EXP AMP摦嶌偱丄Vref偑傜傒偺Q5偺Vbe偼曄壔偼LOG 摦嶌丅偙傟偑Q3偺儀乕僗偵偮側偑偭偰偄傞偑偙傟偑Q3偺Vbe偵懳偟偰偼尭嶼曽岦偵摥偔丅 4:Q3偼AntilogAMP偱Vbe3偲Ic3偺娭學偼EXP摦嶌丅RC4200偺摦嶌偲摨條偵乮Vcv * Vt / Vz )偲偄偆儕僯傾側multiplier偺摦嶌偲側傝嵟廔揑偵偼Iout = It -Icv *( It / Iz )偵側傞偺偱偟傚偆偐丠丅偲偄偆偙偲偼(Vcv * Vt ) 偵懳偟偰 Scale挷惍梫慺偑V倸偱捯咫偑偁偄傑偡偹丅 CES偺奣擮恾偱偼OPAMP傪巊偭偨揹埑-揹棳夞楬乮掕揹棳)偱偡偑ALFA斉偼ALFA斉偼揹埑-揹棳曄姺偼僄儈僼僅儘偺掕揹棳夞楬偲偄偆奣擮恾偵側偭偰偄傑偡丅 IC側傜偱偼偺峔惉偲偄偆偐IC壔偡傞埲慜偺VCO偱偼拞乆偙偺傛偆側暔偼傒偐偗傑偣傫偑Hillwood偺SY1800偺antilog偼偦傟偵嬤偄曽朄傪庢偭偰偄傑偡偑忔嶼婍偱偼側偔KBD CV夞楬偺ref揹埑偲偄偆幚幙忔嶼婍偵憡摉偡傞Vt偵斾椺偡傞揹尮傪巊偭偰偄傑偟偨丅 摨帪婜偺僥僋僯僋僗偺analog mono synth SY-1010傕摨條偺曽幃偱SPAN曗彏傪偟偰偄偨傛偆偱偡丅 奺Tr.偼1徾尷偺multiplier偺恾偱偼C-E娫偑OP AMP偺FB儖乕僾偵擖傝掕揹棳偱僪儔僀僽偝傟偰偄傑偟偨偑忋婰偺摍壙夞楬偵偍偄偰傕C-E娫偑掕揹棳偱僪儔僀僽偝傟偰偄傞偙偲偵戙傢傝偼偁傝傑偣傫偺偱Vbe偺曄壔偼antilog Tr. Q3埲奜偼LOG曄壔偲偄偆偙偲偱偡丅偡側傢偪傎傏1徾尷偺multiplier偲偟偰偺摦嶌偩偲巚偄傑偡丅

CEM偺VCO偼偙偺CEM3340(3345)偲CEM3394媦傃CEM3374偑偁傝傑偡丅丂CEM3394偼3340偲摨曽幃偺scale曗彏偱偡偑CEM3374偼scale曗彏夞楬(multiplier)偼搵嵹偝傟偰偄偢偐傢傝偵Vt弌椡偺壏搙僙儞僒乕偑晅偄偰偍傝偙傟傪棙梡偟偰奜晹偱摨條偺張棟傪偟偰壓偝偄偲偄偆巇條偱偡丅丂帪戙揑偵3374偼computer controlled傪慜採偲偟偰偄傞偺偱soft ware 張棟偐 扨弮偵偼DAC偺Vref偵偙傟傪偮側偄偱 tempco multiplier傪幚尰偟偰偔傟偲偄偆偙偲側偺偱偟傚偆丅CES Applcaton Note APCEM-001偵巊梡椺偑嵹偭偰偄傑偡丅偦偆偱側偔弮analog偱峴偆応崌偼忋婰偺傛偆側1徾尷偺忔嶼婍(RC4200側偳乯傪巊偆偙偲偵側傝傑偡偑柺搢側偺偱捠忢偼CPU張棟偑慜採偱偡丅儊乕僇偺惢昳偱偼analog multiplier傪巊偭偨椺偼側偄偺偱偼側偄偐偲巚傢傟傑偡乮枹妋擣乯丅

|

偦偺懠CEM3340偱廳梫偦偆側PIN傪尒偰傒傞偲丄

3: 儅僀僫僗揹尮擖椡

6.5V偺僣僃僫乕僟僀僆乕僪偑撪晹偵偁傞偺偱偙傟傪棙梡偡傞応崌偼儅僀僫僗揹尮偲 偙偺抂巕娫偵揹棳惂尷掞峈傪偮偗傞丅 報壛揹埑偑-6V埲壓偺応崌偼僣僃僫乕偑柍岠 偲側傝報壛揹埑偑捈愙桳岠丅丂偡側傢偪尦乆CEM3340偼+/-摨偠揹尮揹埑偺IC偱偼側偄偑堦斒揑側+/-摨偠揹埑偺揹尮偱傕懳墳OK偵側傞傛偆側巇條偵側偭偰偄傞偲偄偆偙偲偱偟傚偆丅丂偱偡偐傜昡壙儃乕僪夞楬偵偍偄偰傕-5V偑巊偊傞偺側傜偦傟傪巊偭偰偔傟偲偄偆偙偲偱+15V/-5V偵側偭偰偄傞偺偱偟傚偆丅

4: 嬮宍攇弌椡

0--12V (Vcc15V帪)丂偙偺弌椡偼NPN偺僆乕僾儞僄儈僢僞側偺偱僾儖僟僂儞掞峈傪偮偗傞丅 丂偪側傒偵嶰妏攇偼 0-- 5V丄嫎攇偼 0 --10V弌椡丅

07:崅堟岆嵎曗彏梡偺揹棳弌椡

崅堟曗彏偑昁梫側偺偼 antilog 僩儔儞僕僗僞偺 僄儈僢僞僶儖僋掞峈偺塭嬁偍傛傃 僐儞僷儗乕僞偺崅堟偱偺ON/OFF帪娫偺塭嬁側偺偱偦傟傪曗惓偡傞偨傔偙偺抂巕弌椡(*1)傪summing node偵擖椡偡傞偙偲偵傛偭偰曗惓偡傞丅丂偙偺抂巕偲GND娫偵敿屌偺VR傪偄傟偰敿屌偺恀傫拞偺抂巕偵掞峈傪偮偗偰 summing node偵擖椡丅丂偍偍傓偹5KHz偁偨傝偐傜崅堟岆嵎偺塭嬁偑偁傞傜偟偄丅

*1:僨乕僞乕僔乕僩偺恾偵偼antilog梡偺僩儔儞僕僗僞偲僷儔偭偰晅偗偰偁傞傕偆堦偮偺antilog 僩儔儞僕僗僞偺揹棳弌椡偑偙偺抂巕偵側偭偰偄傑偡丅

16:+揹尮抂巕

+10V偐傜+18V傑偱偲側偭偰偄偰偍偍傓偹 +12V偐+15V傪巊梡偟偰偄傞傛偆偱偡丅丂15V偑巊偊傞側傜悇彠抣偵廬偭偰15V偵偡傞偺偑柍擄偱偟傚偆丅

CEM3340偼+揹尮抂巕丂-揹尮抂巕娫偱MAX24V側偺偱丂+15V, -5V偱巊偆偐 +/-15V偲偟偰儅僀僫僗抂巕偼揹棳惂尷掞峈傪擖傟偰幚幙-6.5V偱巊偆傛偆側応崌偑奺幮偺夞楬恾傪尒偰傕懡偄傛偆偱偡丅

datasheet傗 service manual傪尒偨尷傝偱偼偍偍傓偹data sheet 弨嫆偺夞楬丄掕悢偱 傛偄姶偠偑偟傑偡丅

掞峈抣偺愝掕

Rz: 24K +10K VR 嬥旂

Rt: 5.6K丂丂嬥旂

Rs: 1.8K丂丂嬥旂

Rr: 1.5M丂丂嬥旂

Rhft: 1M 丂20K VR丂嬥旂

|

庤帩偪偺嬥旂偱偼懌傝側偄傕偺偑偄偔偮偐偁傞偺偱丄嬥旂偺攦偄偨偟傪偡傋偔僱僢僩偱廐寧偺100杮嬥旂乮300墌乯偺抣傪妋擣偡傞偲1M埲忋偺掞峈抣偑偁傝傑偣傫丅丂1M偼偍傠偐500K埲忋偺抣傕側偄傛偆偱偡丅丂側傜偽偲愮愇傪尒偰傒傞偲嬥旂偺扨懱攧傝偑1杮30墌丄1M埲忋偼側傫偲50墌偩偲偐丅丂CEM3340偑婎杮偨偩側偺偱掞峈偺崅偝偑傾儞僶儔儞僗側傛偆側婥傕偟傑偡偑偟偐偨偑側偄偺偱媣乆偵廐梩偵晹昳偺攦弌偟偱偡丅

傑偢偼廐寧偱24K, 5.6K, 1.8K偺100杮嬥旂傪峸擖丅丂偦偺屻丄愮愇偵峴偭偰偺嬥旂偺扞傪尒傞偲側傫偲1杮 10墌丅丂僱僢僩偵彂偄偰偁偭偨偺偲堘偆丅丂偙傟側傜100杮僙僢僩傪攦傢偢偵奺掞峈傪扨昳*10掱搙攦偭偨傎偆偑傛偐偭偨偲屻夨丅丂 妋偐偵愄偺婰壇偱偼愮愇偺扨昳嬥旂偼1屄10墌偱偁偭偨偼偢偱丄30墌偼偍偐偟偄偲堦弖巚偭偨偺偩偑丅 1M傑偱側傜10墌偱攦偊傞傛偆偱偡丅丂扐偟1M傪挻偊傞掞峈偼傗偼傝50墌偟偰偟傑偆丅丂 偁傑傝偵崅偄偺偱働僠偭偰 1.5M*4傪攦偆丅丂攦偄廔傢偭偰偐傜儅儖僣偵傕掞峈偑抲偄偰偁偭偨偲巚偄弌偟儅儖僣偺掞峈扞傪尒傞偲側傫偲1.5M偑10墌偱偁偭偨丅丂扐偟3M偼傗偼傝偙偙偱傕50墌傕偡傞丅丂傑偨傑偨屻夨偡傞傕1.5M傪20屄峸擖丅丂挿傜偔晹昳峸擖傪偟偰偄側偐偭偨偺偱姩偑嫸偭偨姶偠丅丂幚幙1000墌偔傜偄懝偟偨姶偠偱偔傗偟偄丅 Vref傪亄5V偲偡傟偽1.5M偺掞峈偼500K偱嵪傓偙偲偵側傞偺偱偦偺曽偑偄偄偐偲傕巚偄傑偡偑丄儊乕僇乕摍偺夞楬傪尒偰傕扨弮偵+15V偐傜偲偭偰偄傑偡丅

屻擔択:

|

CEM3340偺摦嶌

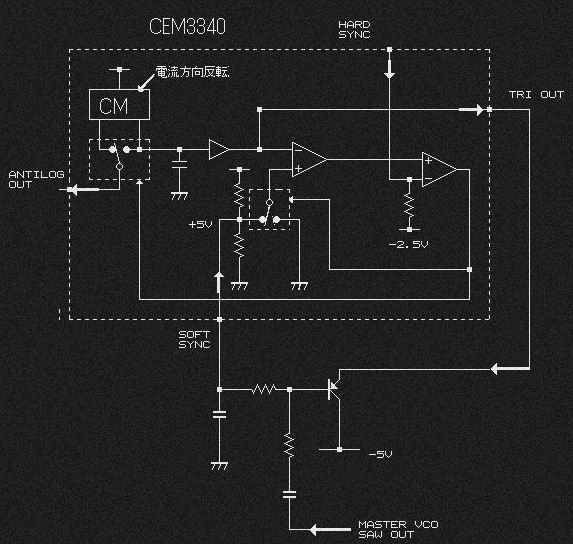

CEM3340偼 堦斒揑側VCO偑SAW攇傪尮攇宍偲偟偰敪怳偡傞偺偵懳偟偰丄嶰妏攇傪 尮攇宍偲偟偰惗惉偟丄TRI-SAW converter偵傛傝 SAW攇傪摼傞VCO偲側偭偰偄傑偡丅 (壓恾偵偍偄偰2偭偺SW偵傛傝丄掕揹棳尮偺曽岦偲丄僐儞僷儗乕僞偺斾妑婎弨揹埑傪 5V偲0V偵愗傝偐偊傞)

CEM3340偺antilog偼 capacitor偐傜揹棳傪揻偒弌偡(曻揹)曽岦偑惓曽岦側偺偱丄capacitor傪廩揹偡傞帪偼僇儗儞僩儈儔乕(CM)傪夘偟偰antilog偵愙懕偝傟偰偄傞抂巕偲偼斀懳偺僇儗儞僩儈儔乕偺抂巕偑capacitor傪廩揹偡傞傛偆側峔憿偵側偭偰偄傑偡丅丂曻揹帪偼CM偼摦嶌偣偢 antilog 偵捈愙 capacitor偑愙懕偝傟傞傛偆偵 SW偱愗傝懼偊傞偙偲偵傛傝capacitor揹埑偑忋徃丄壓崀偟傑偡丅 SW偺僐儞僩儘乕儖偼2抜峔惉偺僐儞僷儗乕僞偺屻抜偺僐儞僷儗乕僞弌椡偱峴傢傟傑偡丅 嶰妏攇忋徃帪偼1抜栚偺僐儞僷儗乕僞偺偟偒偄抣偑+5V偱丄capacitor偺廩揹偑5V傪挻偊傞偲僐儞僷儗乕僞偺嬌惈偑斀揮偟偰偦傟傪庴偗偰屻抜偺僐儞僷儗乕僞弌椡偑忋婰 SW傪愗傝懼偊傞偲偲傕偵1抜栚偺僐儞僷儗乕僞帺恎偺偟偒偄抣傪0V偵偟傑偡丅

CEM3340偺sync

soft sync:

--------------

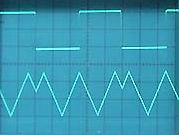

嶰妏攇偑忋徃僇乕僽偺忬懺帪丄soft sync in偵嬮宍攇偺棫壓傝偺攇宍偑擖傞偲僐儞僷儗乕僞偺鑷抣偑堦弖儅僀僫僗偵側傞偺偱嶰妏攇偑壓崀僇乕僽偵慗堏偟傑偡丅丂偡側傢偪嶰妏攇偑5V偵払偟偰偄側偄傑傑偱壓崀偵岦偐偆偺偱偦偺暘丄廃婜偑抁偔側傞偲偄偆偙偲偱偡丅丂忋徃僇乕僽帪側傜偳傫側僞僀儈儞僌偱傕OK偲偄偆傢偗偱偼側偔幚應偱偼嶰妏攇偺怳暆偑偍偍傛偦4V(*1)偔傜偄傛傝戝偒偄帪偩偗僐儞僷儗乕僞偑壱摦偡傞傛偆偱偡丅

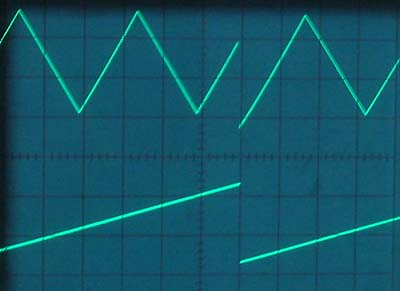

僨乕僞乕僔乕僩偵偼攇宍偑帵偝傟偰偄傑偣傫偑丄soft sync偼攇宍偑曄壔偟側偄偺偑慜採偩偐傜偱偟傚偆偐丅丂幚嵺偼偨偲偊偽憡庤偺master VCO偺廃攇悢偑庒姳崅偗傟偽3340偺嶰妏攇偑5V傑偱払偟側偄埵抲偱曽岦斀揮偑婲偒傞偺偱嶰妏攇偺怳暆偑彫偝偔側傝傑偡丅丂 偦偺帪丄嶰妏攇偺応崌偼攇宍偺曄宍偼偁傝傑偣傫偑丄嫎攇偼宍偑曄宍偟丄嬮宍攇偼僷儖僗暆偑彮偟曄傢傝傑偡丅

*1:棫壓傝偺嬮宍攇偑0.001uF偺capacitor傪夘偟偰soft sync抂巕偵壛傢偭偨帪丄捠忢5V偺鑷抣揹埑偑弖娫4V掱搙偵棊偪傞偲偄偆偙偲側偺偱偟傚偆偐丠丅丂僨乕僞乕僔乕僩偺夞楬偐傜偼扨弮偵偼0V掱搙偵棊偪偦偆側偺偱偡偑.....

恾偺傛偆偵soft sync偑偐偐偭偰偄傞偲偄偆偙偲偼master VCO偺嬮宍攇偺棫壓傝偺僞僀儈儞僌偲slave VCO偺3340偺嶰妏攇偺曽岦揮姺僞僀儈儞僌偑堦抳偡傞偲偄偆偙偲偱丄埵憡傕儘僢僋偝傟傑偡丅 丂嫎攇偼攇宍偑曄宍偟偰偄傑偡丅丂帪娫偑抁弅偝傟偨暘丄悅捈忋徃偟摨偠孹偒偱忋徃偡傞偺偱 嫎攇偺僗儘乕僾偑偢傟偰偄傑偡丅丂傑偨master VCO偲偺廃攇悢偺娭學丄埵憡娭學偵傛偭偰偼晹暘揑偵嶰妏攇偺怳暆偑晄懙偄側攇宍偵側傞応崌傕偁傝傑偡丅

hard sync:

--------------

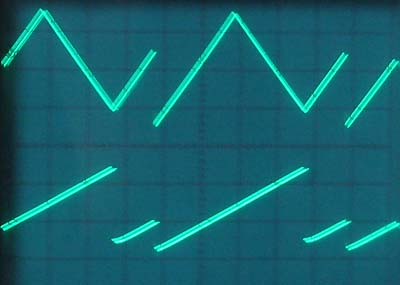

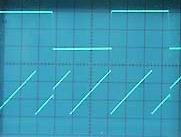

壓恾偵hard sync傪偐偗偨帪偺嶰妏攇偺攇宍傪帵偟傑偡丅丂sync傪偐偗偨僞僀儈儞僌偱婎杮丄嶰妏攇偺曽岦斀揮傪偡傞偩偗偱偡丅丂hard sync in偵僾儔僗偺僷儖僗傪梌偊傞偲positive sync,儅僀僫僗偺僷儖僗傪梌偊傞偲negative sync偱偡偑丄忋徃嬫娫偱偺傒偟偐positive sync偼偐偐傜側偄偟壓崀嬫娫偱偺傒偟偐 negative sync偼偐偐傝傑偣傫丅

* positive hard sync

丂

丂

* negative hard sync

忋婰偺攇宍傪尒偰傕嫎攇偺堦晹偵僷儖僗攇偑壛傢偭偨傛偆側攇宍側偺偱壒怓傕嫎攇偲嬮宍攇偑崿偞偭偨傛偆側丄捠忢偺sync偲偼彮偟堎側傞壒怓偱偡丅丂傑偨嶰妏攇偺曽傕娫偵彫偝側嶰妏攇偑擖偭偨攇宍偵側傞偨傔壒怓揑偵偼僼僅儖儅儞僩僂僃乕僽揑側僉儍儔僋僞乕傪帩偪傑偡丅

modular synth傪彍偔儊乕僇乕惢偺synth偱CEM3340偺soft sync傪搵嵹偟偨婡庬偼傒偨偙偲偑偁傝傑偣傫丅丂傑偨CEM3340偺hard sync偼嶰妏攇偺曽岦揮姺偲偄偆彮乆摿庩側曽幃側偺偱丄晛捠偺hardsync傪幚尰偟偨偄応崌偼negative sync偺傒偑桳岠偵側傝丄偐偮sync 僷儖僗偱嶰妏攇偺怳暆傪嫮惂揑偵0偵棊偲偡夞楬傪晅壛偟偰conventional hard sync傪幚尰偡傞傛偆偵偟傑偡丅

|

* conventional hard sync *

僨乕僞乕僔乕僩偵偼埲壓偺傛偆側夞楬傪晅壛偡傞傛偆偵彂偐傟偰偍傝丄prophet5, OB8傪弶傔偲偡傞儊乕僇惢偺synth偱嵦梡偝傟偰偄傑偡丅

master VCO偺 SAW攇偺棫壓傝(儅僀僫僗偺旝暘僷儖僗 )偱 PNP Tr 傪 ON偝偣 TRI攇傪嫮惂揑偵0V偵偝偣傞偲偲傕偵soft sync抂巕偵傕棫壓傝偺僷儖僗傪梌偊撪晹僐儞僷儗乕僞傕嫮rrrrr惂揑偵斀揮偝偣 儕僙僢僩屻偼capacitor偺揹埵偑0偐傜忋徃偡傞傛偆偵偡傞丅 CEM3340偑恾偺夞楬偺捠傝偱偁傟偽 TRI攇偺弌椡偼0(*1)偵側偭偰傕丄capacitor偺廩揹偑弖帪偵0偵側傞宱楬偑懚嵼偟側偄丅丂偍偦傜偔TRI OUT偑僔儑乕僩偝傟傟偽capacitor偺屻偺buffer偑buffer偲偟偰婡擻偟側偔側傝(*2)TRI OUT丄PNP偺 C-E娫宱桼偱媫懍曻揹偡傞偺偱偟傚偆丅

*1: 幚嵺偼-0.6V掱搙偵側偭偰偄傞丅

master VCO偺 SAW攇偺棫壓傝偱 pnp Tr 傪 ON偝偣 TRI攇傪嫮惂揑偵0V(-0.6V)偵偝偣傞偺傒丅丂僐儞僷儗乕僞偼慜偺忬懺傪曐帩偟偰偄傞偺偱儕僙僢僩屻傕capacitor偺揹埵偼0(-0.6V)偐傜忋徃丅

|

|

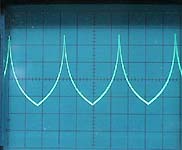

SELF MOD

Linear FM in 偵帺暘帺恎偺攇宍傪 FB偝偣偰 Self Modulation傪幚峴偟偨寢壥傪埲壓偵帵偟傑偡丅

忋恾偺(source,mod=TRI)偺働乕僗偼PAIA偺 Hyper Flanger偺BBD clock modulation攇宍偵巊傢傟偰偄傑偡丅

|

|

* CEM3340偲3345偺堘偄偼丠

datasheet偵偼3340偲3345偑彂偐傟偰偄傑偡丅丂儊乕僇惢偺 synth傗DIY婰帠偱偼3340偑巊傢傟偰偍傝3345偑巊傢傟偰偄傞偙偲偼傑偢柍偄偱偡丅丂3340偑16PIN偵懳偟偰3345偼18PIN偲側偭偰偄傑偡丅丂捛壛偝傟偨PIN偺婡擻偼

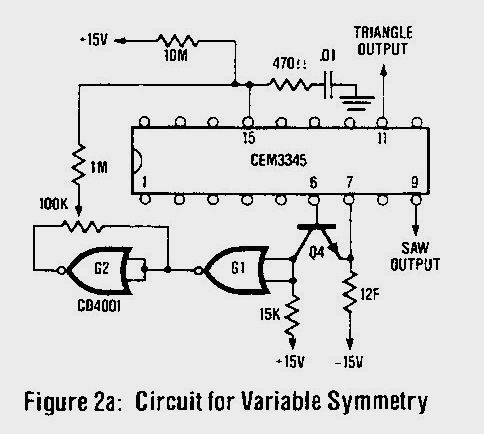

1: antilog amp偺曅曽偺儀乕僗偑撪晹偱 GND偵屌掕偝傟偰偄傞(3340)

2: 3345偼1抜栚(soft sync懁偺)偺僐儞僷儗乕僞弌椡偑buffer晅偒偱7斣PIN偵 data sheet傪尒偰傕3340偲3345偺堘偄偵偮偄偰偼摿偵柧婰偝傟偰偄側偄傛偆側偺偱徻嵶偼傢偐傝傑偣傫丅丂antilog偺寢慄偑奜晹偵弌偰偄偨曽偑墳梡偼偒偔偱偟傚偆丅丂僐儞僷儗乕僞偺弌椡偑弌偰偄傟偽壗偐偵棙梡偱偒傞偺偐丅 news letter偺 synth source偵偼捛壛偝傟偨PIN傪棙梡偟偨嫽枴怺偄婰帠偑宖嵹偝傟偰偄傑偟偨丅丂堦偮偼 analog FM壒尮傪幚尰偡傞偨傔偵偼昁梫側Through Zero VCO丄傕偆堦偮偼 TRI攇偺懳徧惈傪壜曄偱偒傞婡擻偱偡丅丂偳偪傜傕忋婰偺(2)偺崁栚偵偁傞7斣PIN傪偭棙梡偟偨暔偱偡丅 嶰妏攇傪尮攇宍偲偟偰惗惉偡傞VCO側傜偱偼偺墳梡椺偱偡偑CEM3345帺懱偲偰傕儅僀僫乕側VCO偱偡丅梫偼CES偺IC偼奼挘惈偑崅偄偲偄偆偙偲偱偟傚偆偐丅

|